## Chapter 5

# The DEC PDP-8

### Introduction<sup>1</sup>

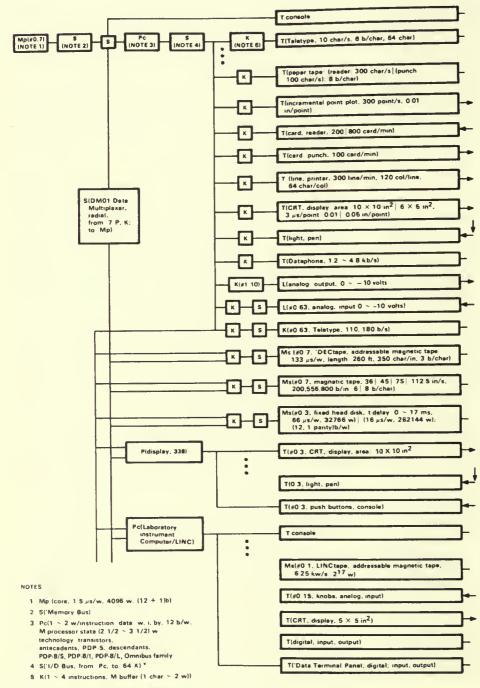

The PDP-8 is a single-address, 12-bit-word computer of the second generation. It is designed for task environments with minimum arithmetic computing and small Mp requirements. For example, it can be used to control laboratory devices, such as gas chromotographs or sampling oscilloscopes. Together with special T's, it is programmed to be a laboratory instrument, such as a pulse height analyzer or a spectrum analyzer. These applications are typical of the laboratory and process control requirements for which the machine was designed. As another example, it can serve as a message concentrator by controlling telephone lines to which typewriters and Teletypes are attached. The computer occasionally stands alone as a small-scale general-purpose computer. Most recently it was introduced as a small-scale general-purpose timesharing system, based on work at Carnegie-Mellon University and DEC. It is used as a KT(display) when it has a P(display; '338); this C is discussed in Chap. 25. The PDP-8 has achieved a production status formerly reserved for IBM computers; about 5,000 have been constructed.

PDP-8 differs from the character-oriented 8-bit computer in Chap. 10; it is not unlike the 16-bit computers, such as the IBM 1800 in Chap. 33. The PDP-8 is typical of several 12-bit computers: the early CDC-160 series (1960), CDC-6600 Peripheral and Control Processor (Chap. 39), the SDS-92, M.I.T. Lincoln Laboratory's Laboratory Instrument Computer LINC (1963), Washington University's Programmed Console (1967), and the SCC 650 (1966).

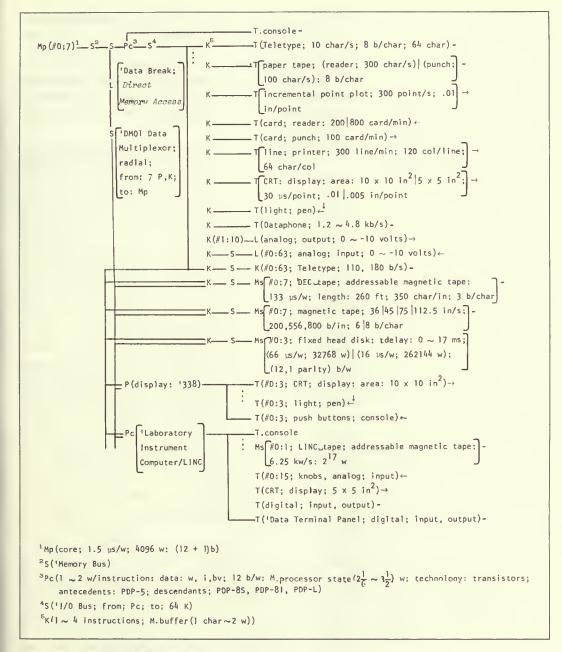

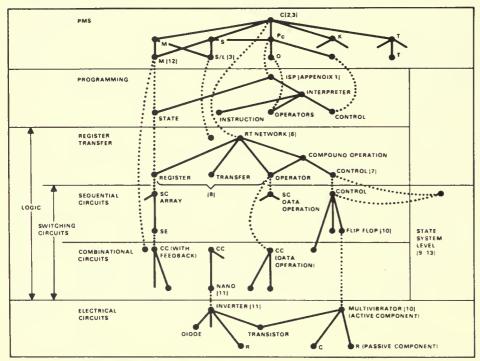

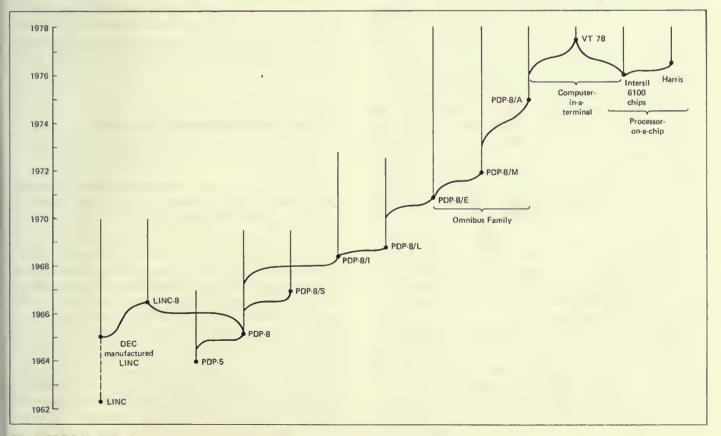

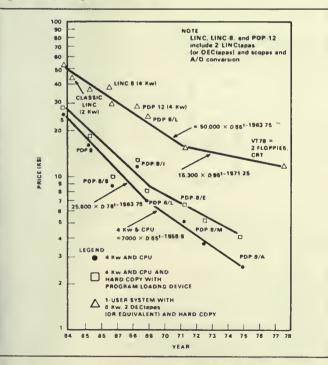

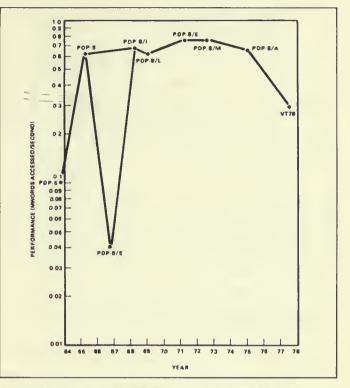

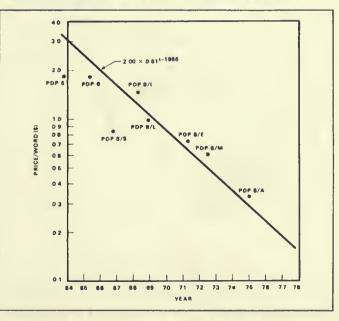

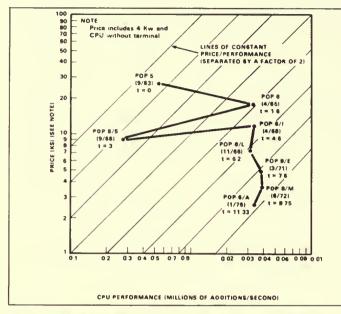

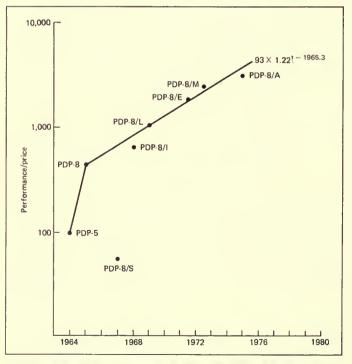

The PDP-5 (transistor, 1963), PDP-8 (1965), PDP-8/S (serial, 1966) and PDP-8/I (integrated circuit, 1968), PDP-8/L (integrated circuit, 1968) constitute a series of computers based on evolving technology. All of these have identical ISP's. Their PMS structures are nearly identical, and all components other than Pc and Mp are compatible throughout the series. The LINC-8-338 PMS structure is presented in Fig. 1. A cost performance tradeoff took place in the PDP-8 (parallel-by-word arithmetic) and PDP-8/S (serial-by-bit arithmetic) implementations. A PDP-8/S is one-fifteenth of a PDP-8 at one-half the cost. The performance factors can be attributed to 8/1.5 or 5.3 for Mp speed and a factor of about 3 for logical organization, even though the same 2-megahertz logic clock is used in both cases. The PDP-8 is about 6.7 times a PDP-5.

<sup>1</sup>The initials in the title stand for Digital Equipment Corporation Programmed Data Processor. The ISP of the PDP-8 Pc is about the most trivial in the book. It has only a few data operators, namely,  $\leftarrow$ , +, - (negate),  $\neg$ ,  $\land$ , / 2,  $\times$  2, (optional)  $\times$ , /, and normalize. It operates on words, integers, and boolean vectors. However, there are microcoded instructions, which allow compound instructions to be formed in a single instruction.

The computer is straightforward and illustrates the levels discussed in Chap. I. We can easily look at it from the "top down." The C in PMS notation is

```

C('PDP-8; technology:transistors; 12 b/w;

descendants:'PDP-8/S, 'PDP-8/I, 'PDP-8/L;

antecedents: 'PDP-5;

Mp(core; \#0.7; 4096 w; tc:1.5 \mus/w);

Pc(Mps(2 \sim 4 w);

instruction length:1|2 w

address/instruction:1;

operations on data/od:(\leftarrow, +, \neg, \land, -(negate), \times 2,

/2, +1)

optional operations: (\times, /, \text{normalize});

data-types:word, integer, boolean vector;

operations for data access:4);

P(display; '338);

P(c; 'LINC);

S('I/O Bus; I Pc; 64 K);

Ms(disk, 'DECtape, magnetic tape);

T(paper tape, card, analog, cathode-ray tube))

```

## ISP

The ISP is presented in Appendix I of this chapter (including the optional Extended Arithmetic Element/EAE). The 2<sup>12</sup>-word Mp is divided into 32 fixed-length pages of 128 words each. Address calculation is based on references to the first page, Page\_0, or to the current page of the Program Counter/PC. The effective-address calculation procedure provides for both direct and indirect reference to either the current page or the first page. This scheme allows a 7-bit address to specify local page addresses.

A  $2^{15}$ -word Mp is available on the PDP-8, but addressing greater than  $2^{12}$  words is comparatively inefficient. In the extended range, two 3-bit registers, the Program Field and Data Field Registers, select which of the eight  $2^{12}$ -word blocks are being actively addressed as program and data.

There is an array of eight registers, called the Auto\_index registers, which resides in Page\_0. This array (Auto\_index[0:  $11]\langle 0:7\rangle := M[10_8:17_8]\langle 0:11\rangle$ ) possesses the useful property that whenever an indirect reference is made to it, a I is first added

to its contents. (That is, there is a side effect to referencing.) Thus, address integers in the register can select the next member of a vector or string for accessing.

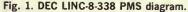

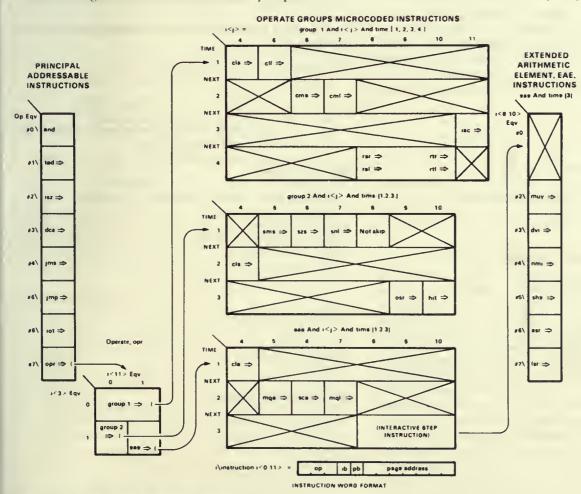

The instruction-set-execution definition can also be presented as a decoding diagram or tree (Fig. 2). Here, each block represents an encoding of bits in the instruction word. A decoding diagram allows one more descriptive dimension than the conventional, linear ISP description, revealing the assignment of bits to the instruction. Figure 2 still requires ISP descriptions for Mp, Mps, the instruction execution, the effective-address calculation, and the interpreter. Diagrams such as Fig. 2 are useful in the ISP design to determine which instruction numbers are to be assigned to names and operations and instructions which are free to be assigned (or encoded).

There are eight basic instructions encoded by 3 bits, that is  $op\langle 0:2 \rangle := i\langle 0:2 \rangle$ , where instruction/ $i\langle 0:11 \rangle$ . Each of the first six instructions (where  $0 \le op < 6$ ) have the 4 address operand determination modes (thus yielding essentially 24 instructions). The first six instructions are:

data transmission:

deposit and clear-accumulator/dca two's complement add to the accumulator/tad

Fig. 2. DEC PDP-8 instruction-decoding diagram.

| binary arithmetic: | two's complement add to the accumu-<br>lator/tad                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------|

| binary boolean:    | and to the accumulator/and                                                                                 |

| program control:   | jump/set program counter/jmp<br>jump to subroutine/jms<br>index memory and skip if results are<br>zero/isz |

Note that the add instruction, tad, is used for both data transmission and arithmetic.

The subroutine-calling instruction, jms, provides a method for transferring a link to the beginning (or head) of the subroutine. In this way arguments can be accessed indirectly, and a return is executed by a jump indirect instruction to the location storing the returned address. This straightforward subroutine-call mechanism, although inexpensive to implement, requires reentrant and recursive subroutine calls to be interpreted by software, rather than by hardware. A stack, as in the DEC 338 (Chap. 25), would be nicer.

The input\_output instruction/iot (:= op = 6) uses the remaining 9 bits of the instruction to specify instructions to input/ output devices. The 6 io\_select bits select 1 of 64 devices. The 3 bits, io\_p1\_bit, io\_p2\_bit, io\_p4\_bit, command the selected device by conditionally providing three pulses in sequence. The instructions to a typical io device are:

io\_pl\_bit  $\rightarrow$  (IO\_skip\_flag[io select]  $\rightarrow$  (PC  $\leftarrow$  PC + 1)) testing a condition of an IO device output to a device input from a device

$io_p4\_bit \rightarrow (Output\_data[io select] \leftarrow AC)$  $io_p2\_bit \rightarrow (AC \leftarrow Input\_data[io select])$

There are three microcoded instruction groups selected by op = 7. The instruction decoding diagram (Fig. 2) and the 1SP description (Appendix 1 of this chapter) show the microinstructions which can be combined in a single instruction. These instructions are: operate group I (:= (op = 7)  $\land \neg_1 i(3)$ ) for operating on the processor state; operate group 2 (:= (op = 7)  $\land (i(3,11) =$  $10_2$ )) for testing the processor state; and the extended arithmetic element group (:= ((op = 7)  $\land (i(3,11) = 11_2)$ )) for multiply, divide, etc. Within each instruction the remaining bits, (4:10) or (4:11), are extended instruction. In this way an instruction is actually programmed (or microcoded). For example, the instruction set\_link  $\rightarrow$ L  $\leftarrow$ 1 is formed by coding the two microinstructions, clear link, next, complement link.

opr\_1

$$\rightarrow$$

(i $\langle 5 \rangle \rightarrow L \leftarrow 0$ ; next

i $\langle 7 \rangle \rightarrow L \leftarrow \neg L \rangle$

Thus, in operate group 1, the instructions clear link, complement link, and set link are formed by coding instruction (5,7) = 10, 01, and 11, respectively. The operate group 2 instruction is used for testing the condition of the Pc state. This instruction uses bits 5, 6, and 8 to code tests for the accumulator. The AC skip conditions are coded ( $0 \sim 7$ ) as never, always,  $=0, \neq 0, <0, \geq 0, <0,$  and >0. If all the nonredundant and useful variations in the two operate groups were available as separate instructions in the manner of the first seven (dca, tad, etc.), there would be approximately  $7 + 12(opr_1) + 10(opr_2) + 6(EAE) = 35$  instructions in the PDP-8.

The optional Extended Arithmetic Element/EAE includes additional Multiplier Quotient/MQ and Shift Counter/SC registers and provides the hardwired operations multiply, divide, logical shift left, arithmetic shift, and normalize. The EAE is defined on the last page of Appendix 1.

### The interrupt scheme

External conditions in the input/output devices can request that Pc be interrupted. Interrupts are allowed if (Interrupt\_state = 1). A request to interrupt clears Interrupt\_state (Interrupt\_state  $\leftarrow 0$ ), and Pc behaves as though a jump to subroutine 0 instruction, jms 0, had been given. A special iot instruction (instruction =  $6001_8$ ) followed by a jump to subroutine indirect to 0 instruction (instruction =  $5200_8$ ) returns Pc to the interruptable state with Interrupt\_state = 1. The program time to save M(processor state/ps) is 6 Mp accesses (9 microseconds), and the time to restore Mps is 9 Mp accesses (13.5 microseconds).

Only one interrupt level is provided in the hardware. If multiple priority levels are desired, programmed polling is required. Most io devices have to interrupt because they do not have a program-controlled enable switch for the interrupt. For multiple devices approximately 3 cycles (4.5  $\mu$ s) are required to poll each interrupter.

### **PMS structure**

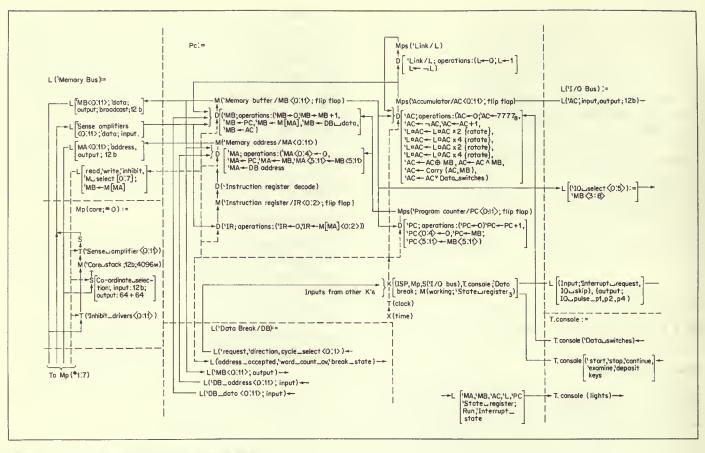

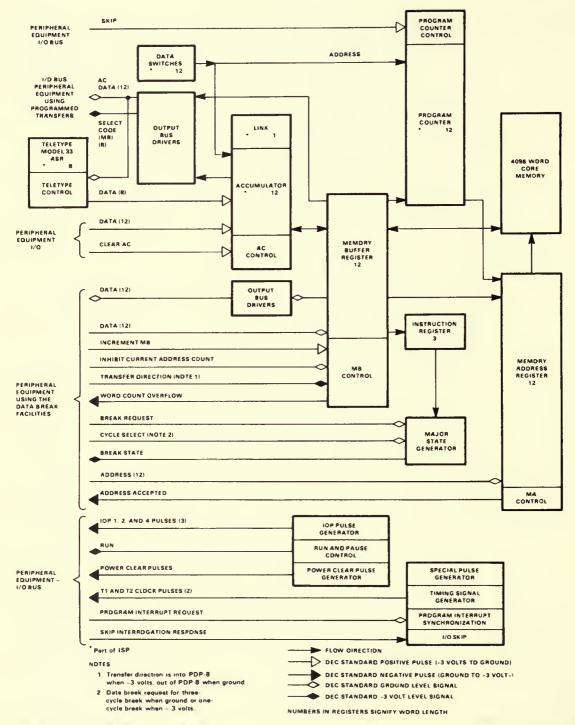

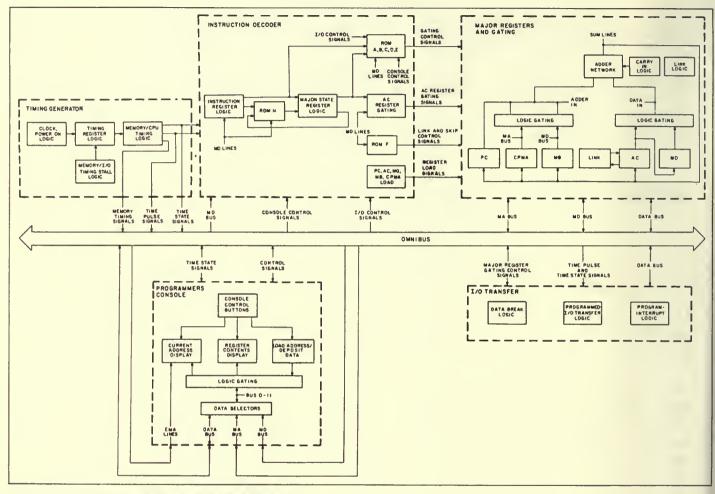

The PMS structure of the LINC-8-338 consisting of a Pc('LINC), Pc('PDP-8), and P.display('338) is shown in Fig. 1. The PDP-8 is just a single Pc. The Pc('LINC) is a very capable Pc with more

instructions than the main Pc. It is available in the structure to interpret programs written for the C('LINC), a computer developed by M.I.T.'s Lincoln Laboratory as a laboratory instrument computer for biomedical and laboratory applications. Because of the rather limited ISP in Pc, one would hardly expect to find all the components present in Fig. 1 in an actual configuration.

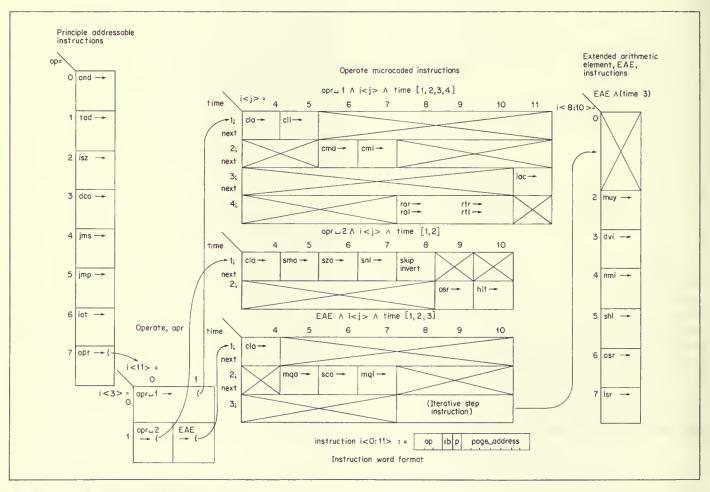

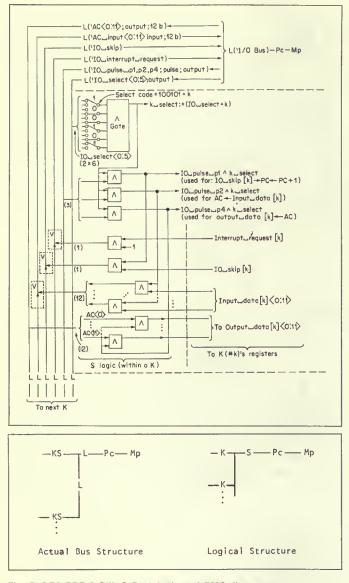

The S between the Mp and the Pc allows eight Mp's. This S is actually S('Memory Bus; 8 Mp; I Pc; (*P requests*); time-multiplexed;  $1.5 \,\mu$ s/w). Thus the switch makes Mp logically equivalent to a single Mp(32768 w). There are two other L's which are connected to the Pc, excluding the T.console. They are L('I/O Bus) and L('Data Break; *Direct Memory Access*). These links become switches when we consider the physical structure. Associated with each device is a switch, and the bus links all the devices; the L('I/O Bus) is really an S('I/O Bus). Each time a K connects to it, the S is included in the K. A simplified PMS diagram (Fig. 3) shows the structure and the logical-physical transformation. Thus, the I/O Bus is

S('I/O Bus; duplex; bus; time-multiplexed, 1 Pc; 64 K; Pc controlled, K requests; t:4.5 μs/w)

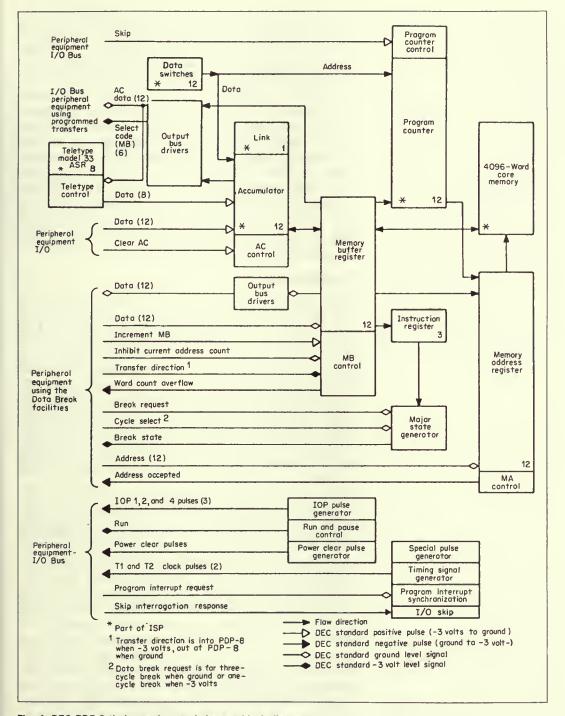

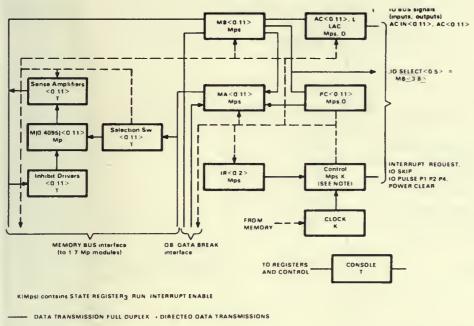

The S('I/O Bus) is the same for the PDP-5, 8, 8/S, 8/I, and 8/L. Hence, any K can be used on any of the above C's. The I/O Bus is the link to the K's for Pc-controlled data transfers. Each word transferred is designated by a Pc instruction. However, the I/O Bus allows a K to request Pc's attention via the interrupt request signal. The Pc polls the K's to find the requesting K if multiple interrupt requests occur. A detailed structure of the Pc-Mp (Fig. 4) shows these L('I/O Bus, 'Data Break) connections to the registers and control in the notation used by DEC. This diagram is essentially a functional block diagram.

The S('I/O Bus) in Fig. 1 is only an abstract representation of

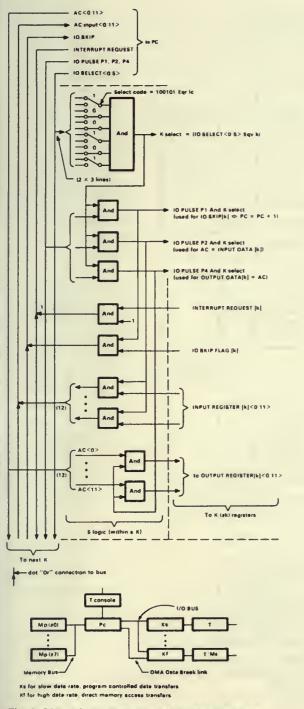

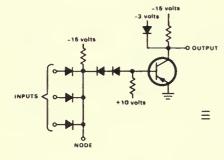

Fig. 3. DEC PDP-8 PMS diagram (simplified).

the structure. Since it is a bus structure, the S can be expanded into L's and simple S's as shown in Fig. 3. The termination of the L in Pc is given in Fig. 3. The corresponding logic at a K is given in Fig. 5 in terms of logic design elements (AND's and OR's). (Fig. 5 also shows the S('I/O Bus) structure of Figs. 1 and 3). The operation of S('I/O Bus) shown in Fig. 5 starts when Pc sends a signal to select (or address) a particular K, using the IO\_select (0.5) signals to form a 6-bit code to which K responds. Each K is hardwired to respond to a unique code. The local control, K[i], select signal is then used to form three local commands when ANDed with the three iot command lines from Pc, io\_p1\_bit, io\_p2\_bit, and io\_p4\_bit. Twelve data bits are transmitted either to or from Pc, indirectly under K's control. This is accomplished by using the AND-OR gates in K for data input to Pc, and the AND gate for data input to K. The data lines are connected to AC as shown in Fig. 4. A single skip input is used so that Pc can test a status bit in K. A K communicates to Pc via the interrupt request line. Any K wanting attention simply ORs its request signal into the interrupt request signal. Program polling in Pc then selects the specific interrupter. Normally, the K signal causing an interrupt is also connected to the skip input.

The L('Data Break; *Direct Memory Access*) provides a direct access path for a P or K to Mp via Pc. The number of access ports to memory can be expanded to eight by using the S('DM0I Data Multiplexer). The S is requested from a P or K. The P or K supplies an Mp address, a read or write access request, and then either accepts or supplies data for the Mp accessed word. In the configuration (Fig. I), P('LINC) and P('338) are connected to S('DM0I) and make requests to Mp for both their instructions and data in the same way as the Pc. The global control of these processor programs is via the S('I/O Bus). The Pc issues start and stop commands, initializes their state, and examines their final state when a program in the other P halts or requires assistance.

When a K is connected to L('Data Break) or to S('DM01 Data Multiplexer), the K only accesses Mp for data. The most complex function these K's carry out is the transfer of a complete block of data between the Mp and an Ms or a T, for example, K('DECtape, disk). A special mode, the three-cycle data break, is controlled by Pc so that a K may request the next word from a queue in Mp. In this mode the next word is taken from the queue (block) in Mp, and a counter is reduced each time K makes a request. With this scheme, a word transfer takes three Mp cycles: one to add one to the block count, one to add one to the address pointer, and one to transmit the word.

The DECtape was derived from M.I.T.'s Lincoln Laboratory LINCtape unit. Data are explicitly addressed by blocks (variable

Fig. 4. DEC PDP-8 timing and control-element block diagram. (Courtesy of Digital Equipment Corporation.)

Fig. 5. DEC PDP-8 S('I/O Bus) logic and PMS diagrams.

but by convention 128 w). Thus information in a block can be replaced or rewritten at random. This operation is unlike queueaccessed tape (conventional IBM format magnetic tape) in which data can be appended only to the end of a file.

The control for the T(telephone) links 64 Teletypes or typewriters to the Pc. The final K which connects to a line is on a bit-serial basis. Since a telephone line sends and receives informa-

tion serially by bit, there are special input/output instructions in the Pc to sample the line and to convert the sampled bits to coded characters. There are 11 bits transmitted per character (although other codings use 7, 7.42, 7.5, and 10 bits per character). Of the 11 bits, there are 3 control, 1 parity, and 7 information bits. The action of the Pc instruction, which is issued  $5 \times 11$  (55) times for every character, is to control the line by forming the 7-bit characters. The instruction is a good example of tradeoff in the hardware/software domain toward almost pure software; the only hardware state associated with a telephone line is a 1-bit register to hold the state of the outgoing line, and a single AND gate to sample the incoming line state. This sampling process requires about 0.3 per cent of Pc-Mp capacity per active line (each of  $10 \sim 15$  char/s). In general, the PDP-8 hardware controls are minimal-in turn fairly elaborate control programs must be used as part of them.

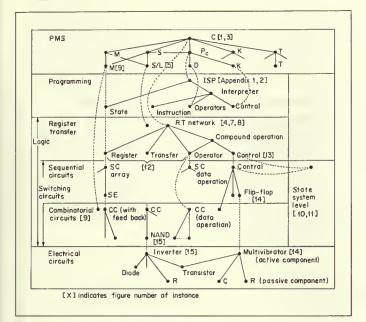

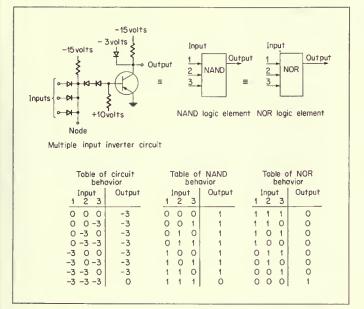

### **Computer levels**

In this section we describe all the systems levels in the PDP-8 computer from the top down. The reader should already have a sketchy knowledge of the PDP-8 because the registers and ISP have been exposed. Here, we wish to clarify how it operates. A map of the hierarchy is given in Fig. 6, starting from PMS to ISP and down through logic design to circuit electronics. These description levels are subdivided to provide more organizational detail. For example, the register-transfer level has the more detailed registers, data operators, functional units, and macro logic of the processor, whereas the next logic level below has sequential and combinational networks, and the sequential and combinatorial elements.

It should be apparent that the relationship of the various description levels constitutes a tree structure where the organizationally complex computer is the top node and each descending description level represents increasing detail (or smaller component size), until the final circuit element level is reached. For simplicity, only a few of the many possible paths through the structural description tree are illustrated. For example, the path showing mechanical parts is missing. The path shown proceeds from the PDP-8 computer to the processor and from there to the arithmetic unit or, more specifically, to the AC register of the arithmetic unit. Next, the macro logic implementing the registertransfer operations and functions for the jth bit of the AC is given; the flip-flops and gates needed for this particular implementation are shown. Finally, on the last segment of the path, come the electronic circuits and components of which flip-flops and NAND gates are constructed.

Fig. 6. DEC PDP-8 hierarchy of descriptions.

#### Abstract representations

Figure 6 also lists some of the methods used to represent the physical computer abstractly at the different description levels. As mentioned previously, only a small part of the PDP-8 description tree is represented here. The many documents, schematics, diagrams, etc., which constitute the complete representation of even this small computer include logic diagrams, wiring lists, circuit schematics and printed-circuit board layout masks, production description diagrams, production parts lists, testing specifications, programs for testing and diagnosing faults, and manuals for modification, production, maintenance, and use. As the discussion continues down the abstract description tree, the reader will observe that the tree conveniently represents the constituent objects of each level and their interconnection at the next highest level. Each level in the abstract-description tree will be described in order.

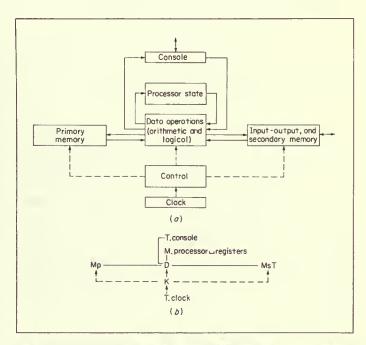

### The PMS level

The simplified PMS structure in Fig. 3 has been reduced from Fig. I. The computer is small enough so that the physical delineation of the PMS components, such as K's and S's, is less pronounced than in larger systems. In fact, in the case of the S('Memory Bus, 'I/O Bus), the S's are actually within the K and Mp, as shown in Fig. 5. The implementation of these switches within the K and Mp was shown in Fig. 5. In Fig. 7 we present a more conventional functional diagram and the equivalent PMS diagram of the computer, with Pc decomposed into K, processor state (Mps), and D. The functional diagram has the same components of the characteristic elementary computer model, namely, K, D, M, and T(input, output). These figures give a somewhat general idea of what processes can occur in the computer, and how information flows, but it is apparent that at least another level is needed to describe the internal structure and behavior of the Mp and Pc. We should look at these primitives (although still together as a C) at the register-transfer level.

### Programming level (ISP)

The ISP interpretation is given in Appendix I of this chapter and is the specification of the programming machine. In addition, it constrains the physical machine's behavior to have a particular ISP. The ISP has been discussed earlier in the chapter.

### **Register-transfer** level

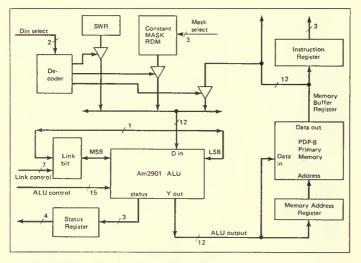

The C can also be represented at the register-transfer level by using PMS. Figure 4 (by DEC) shows the register-transfer level;

Fig. 7. DEC PDP-8 function block and PMS diagrams. (a) Processor functional block diagram. (b) Pc PMS diagram.

Fig. 8. DEC PDP-8 register-transfer-level PMS diagram.

only registers, operations, and L's are important at this level. We still lack information about the conditions under which operations are evoked. Figure 8 is a PMS diagram of Pc-Mp registers. Here we show considerably more detail (although we do not bother with electrical pulse voltages and polarities) than in Fig. 4. We declare the Pc state (including the temporary register) within Pc. The figure also gives the permissible data operations, D, which are permitted on the registers. It should be clear from this that the logical design level for the registers and the operators can easily be reached. The K logic design cannot be reached until we use the programming level constraints (ISP), thus defining the conditions for evoking the data operators.

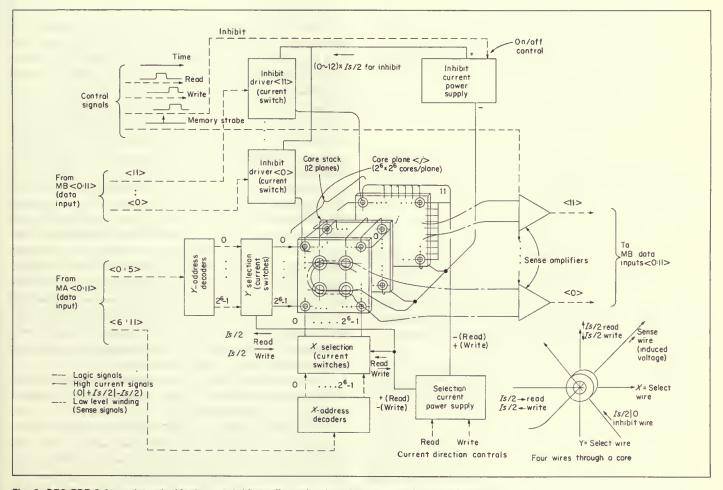

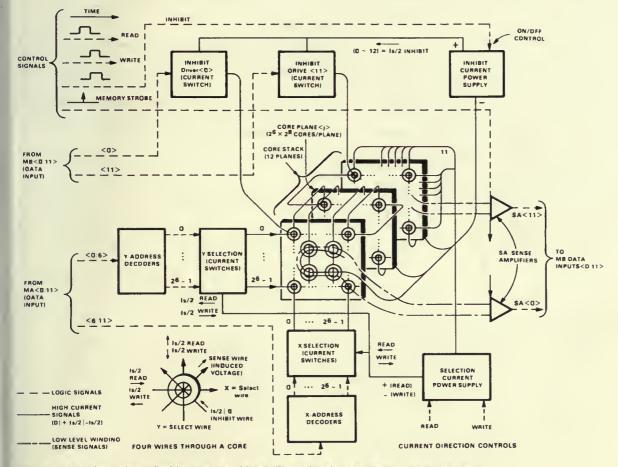

The core memory. The Mp structure is given in Fig. 8. A more detailed block diagram which shows the core stack with its twelve

$64 \times 64$  1-bit core planes is needed. Such a diagram, though still a functional block diagram, takes on some of the aspects of a circuit diagram because a core memory is largely circuit-level details. The Mp (Fig. 9) consists of the component units: the two address decoders (which select 1 each of 64 outputs in the X and Y axis directions of the coincident current memory); selection switches (which transform a coincident logic address into a highcurrent path to switch the magnetic cores); the 12 inhibit drivers (which switch a high current or no current into a plane when either a 0 or 1 is rewritten); 12 sense amplifiers (which take the induced low sense voltage from a selected core from a plane being switched or not switched and transform it into a 1 or 0); and the core stack, an array M[0:7777<sub>8</sub>] $\langle 0:11 \rangle$ . Since this is the only time the Mp is mentioned, Fig. 9 also includes the associated circuitlevel hardware needed in the core-memory operation, such as power supplies, timing, and logic signal level conversion amplifiers. The timing signals are generated within Pc(K) and are shown together with Pc's clock in Fig. 10.

The process of reading a word from memory is:

- 1 A 12-bit selection address is established on the MA $\langle 0:11 \rangle$ address lines, which is 1 of  $10000_8$  (or  $4096_{10}$ ) unique numbers. The upper 6 bits,  $\langle 0:5 \rangle$ , select 1 of 64 groups of Y addresses and the lower 6 bits,  $\langle 6:11 \rangle$ , select 1 of 64 groups of X addresses.

- 2 The read logic signal is made a 1.

- 3 A high-current path flows via the X and Y selection switches. In each of the X and Y directions  $64 \times 12$  cores

have selection current. Only one core in each plane is selected since lx = ly = lswitching/2, and the current at the selected intersection = lx + ly = lswitching.

- 4 If a core is switched to 0 (by having Iswitching amperes through it), then a 1 was present and is read at the output of the plane (bit) sense amplifiers. A sense amplifier receives an input from a winding that threads every core of every bit within a core plane  $[0:7777_8]$ . All 12 cores of the selected word are reset to 0. The sense time at which the sense amplifier is observed is tms (memory strobe), and the strobe in effect creates MB  $\leftarrow$  M[MA].

- 5 The read current is turned off.

Fig. 9. DEC PDP-8 four-wire coincident current (three dimensions) core-memory-logic block diagram.

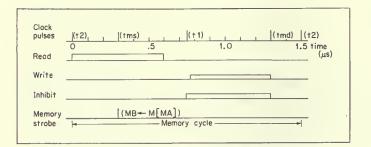

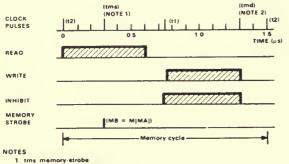

Fig. 10. DEC PDP-8 clock and memory timing diagram.

- 6 The write and inhibit logic signals are turned on. The bit inhibit signal is present or not, depending on whether a 0 or I, respectively, is written into a bit.

- 7 A high-current path flows via the X and Y selection switches, but in an opposite direction to the read case (2 above). If a I is written, no inhibit current is present, and the net current in the selected core is -Iswitching. If a 0 is written, the current is -Iswitching +(Iswitching/2) and the core remains reset.

- 8 The inhibit and write logic signals are turned off, and the memory cycle is completed.

Registers and operations. As Fig. 8 shows, the registers in the Pc cannot be uniquely assigned to a single function. In a minimal machine such as the PDP-8, functional separation is not economical. Thus there are not completely distinct registers and transfer paths for memory, arithmetic, and program and instruction flow. (This sharing complicates understanding of the machine.) However, Fig. 8 clarifies the structure considerably by defining all the registers in Pc (including temporaries). For example, the Memory Buffer/MB is used to hold the word being read from or written to Mp. MB also holds one of the operands for binary operations (for example, AC  $\leftarrow$  AC  $\land$  MB). MB is also used as an extension of the Instruction Register/IR during the instruction interpretation.

The additional registers, not in the ISP, are:

| Memory Buffer/MB(0:11)       | holds memory data,<br>instruction, and oper-<br>ands         |

|------------------------------|--------------------------------------------------------------|

| Memory Address/MA(0:11)      | holds address of word<br>in Mp being accessed                |

| Instruction Register/IR(0:2) | holds the value of<br>current instruction<br>being performed |

| State_register <sub>3</sub>                 | a ternary state register<br>holding the major<br>state of memory cycle<br>being performed |

|---------------------------------------------|-------------------------------------------------------------------------------------------|

| $Fetch/F := (State\_register = 0)$          | memory cycle to<br>fetch instruction                                                      |

| Defer/D/Indirect<br>:= (State_register = I) | memory cycle to get<br>address of operand                                                 |

| Execute/E<br>:= (State_register = 2)        | memory cycle to fetch<br>(store) operand and<br>execute the instruc-<br>tion              |

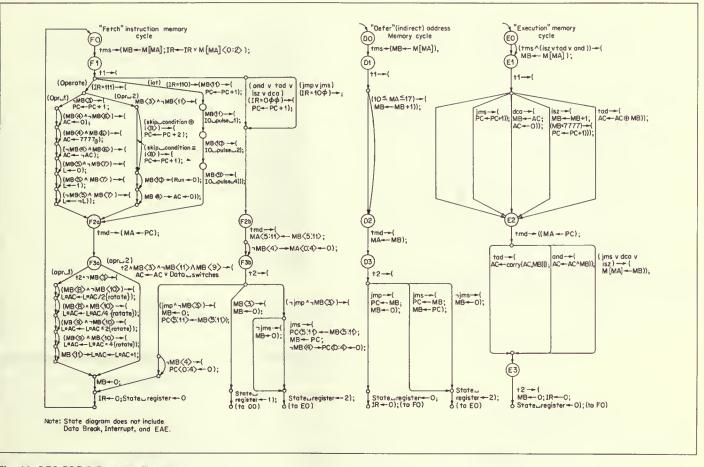

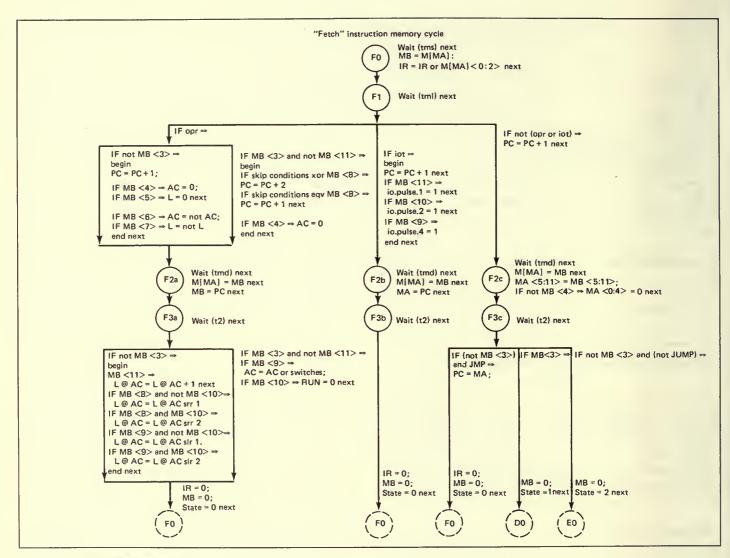

Figure 8 has been concerned with the static definition (or declaration) of the information paths, the operations, and state. The ISP interpretation (Appendix 1) is the specification for the physical machine's behavior. As the temporary hardware registers are added, a more detailed ISP definition could be given in terms of time and temporary registers. Instead, we give a state diagram (Fig. 11) to define the actual Pc which is constrained by both the ISP registers, the temporary registers implied by the implementation, and time. The relationship among the state diagram, the ISP description, and the logic is shown in the hierarchy of Fig. 6. In the relationships of the figures, we observe that the ISP definition does not have all the necessary detail for fully defining a physical Pc. The physical Pc is constrained by actual hardware logic and lower-level details even at the circuit level. For example, a core memory is read by a destructive process and requires a temporary register (MB) to hold the value being rewritten. This is not representable within a single ISP language statement since we define only the nondestructive transfer  $\leftarrow$ , but it can be considered as the two parallel operations  $MB \leftarrow M[MA]$ ;  $M[MA] \leftarrow 0$ . The problem of explaining rewriting of core using ISP is also difficult, because explicit time is not in the ISP language (although we can define clock events, or at least relative time).

The state diagram (Fig. 11) describes the implementation behavior using the registers and register operations (Fig. 8) and the temporary registers declared above.

The implementation is fundamentally Mp-timing-based, as we see from both the state diagram and the times when the four clock signals are generated (Fig. 10). Thus there are three (State\_register = 0,1,2) × 4 (clock), that is, 12 major states, in the implementation. We use the IR to obtain two more states, F2b and F3b,

Fig. 11. DEC PDP-8 Pc state diagram.

for the description. The State\_register values 0, 1, and 2 correspond to fetching, deferring (indirect addressing, i.e., fetching an operand address), and executing (fetching or storing data, then executing) the instruction. The state diagram does not describe the Extended Arithmetic Element/EAE operation, the interrupt state, and the data break states (these add 12 more states). The initialization procedure, including the T.console state diagram, is also not given. One should observe that when t2 occurs at the beginning of the memory cycle, a new State\_register value is selected. The State\_register value is always held for the remainder of the cycle; i.e., only the sequences  $(F0 \rightarrow F1 \rightarrow F2 \rightarrow F3)$  or  $D0 \rightarrow D1 \rightarrow D2 \rightarrow D3$  or  $E0 \rightarrow E1 \rightarrow E2 \rightarrow E3$ ) are permitted.

Figure 8 alludes to Pc(K), that is, the sequential network used for controlling Pc. The inputs and the present state (including clocks) determine the operations to be issued on the registers.

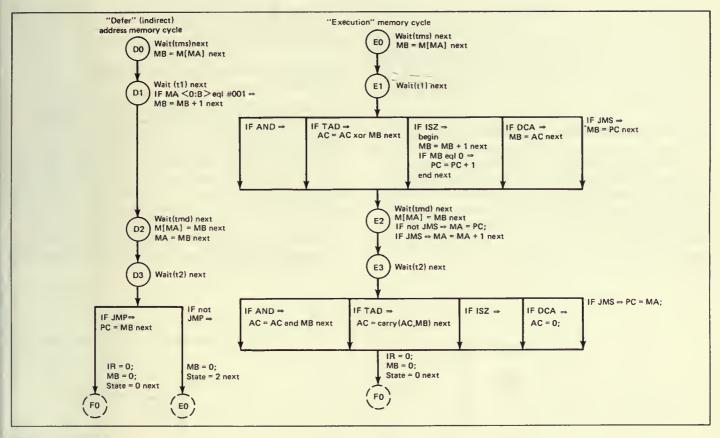

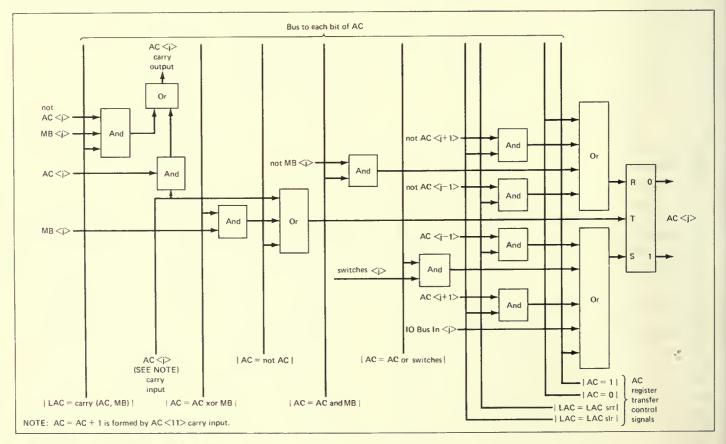

### Logic design level (registers and data operations)

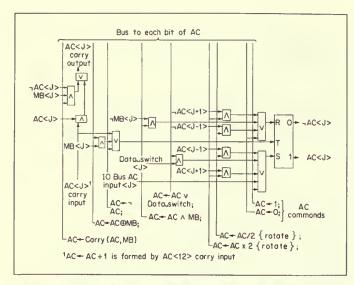

Proceeding from the register-transfer and ISP descriptions, the next level of detail is the logic module. Typical of the level is the 1-bit logic module for an accumulator bit,  $AC\langle j \rangle$ , illustrated in Fig. 12. The horizontal data inputs in the figure are to the logic module from  $AC\langle j \rangle$ ,  $MB\langle j \rangle$ ,  $IO Bus\langle j \rangle$ , and  $Data\_switch\langle j \rangle$ . The vertical control signal inputs command the register operations (i.e., the transfers); they are labeled by their respective ISP operations (for example,  $AC \leftarrow MB \land AC$ ,  $AC \leftarrow AC \times 2$  {rotate}). The sequential network Pc(K) (Fig. 8) generates these control signal inputs.

### Logic design level (Pc control, Pc(K) sequential network)

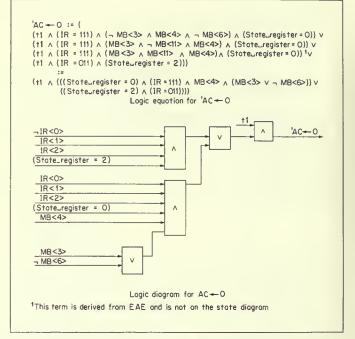

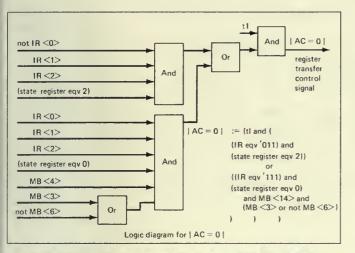

The output signals from the Pc(K) (Fig. 8) can be generated in a straightforward fashion by formulating the boolean expressions

Fig. 12. DEC PDP-8 AC(J) bit register-transfer logic diagram.

Fig. 15. DEC PDP-8 combinational element circuit and logic diagrams.

directly from the state diagram in Fig. 11. For example, the  $AC \leftarrow 0$  control signal is expressed algebraically and with a combinatorial network in Fig. 13. Obviously these boolean output control signals are functions which include the clock, the State\_register, and the states of the arithmetic registers (for example, A = 0, L = 0, etc.). The expressions should be factored and minimized so as to reduce the hardware cost of the control for the interpreter. Although we are rather cavalier about Pc(K), it constitutes about one-half the logic within Pc.

### Circuit level

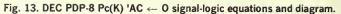

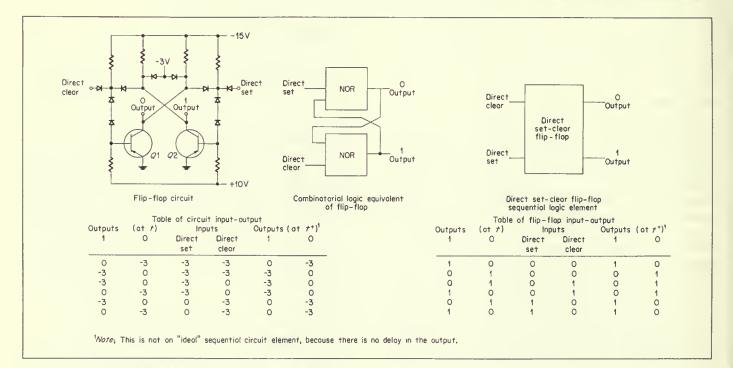

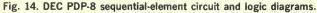

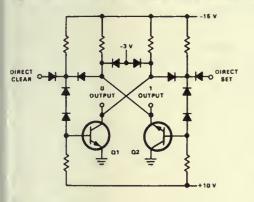

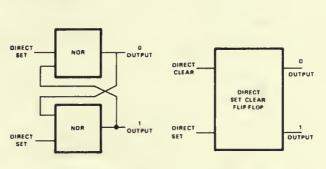

The final level of description is the circuits which form the logic functions of storage (flip-flops) and gating (NAND gates). Figures 14 and 15 illustrate some of these logic devices in detail.

In Fig. 14 a direct set and direct clear flip-flop, a sequentiallogic element, is described in terms of circuit implementation, combinational logic equivalent, a table of its behavior, and its algebraic behavior. Note that this is not an ideal element, because it has no delay and responds directly and immediately to an input. Some idealized sequential logic elements are used in the PDP-8 (but not illustrated), including the RS (Reset-Set), T(Trigger), JK, and D(Delay). A delay in the flip-flops makes them behave in the same way as the ideal primitives in sequentialcircuit theory. The outputs require a series delay,  $\Delta t$ , such that, if the inputs change at time t, the outputs will not change until t +  $\Delta t$ . In fact, the PDP-8 uses capacitor-diode gates at the flipflop inputs to delay the inputs.

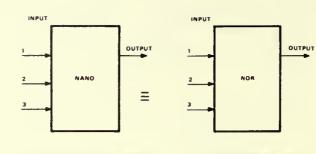

Figure 15 illustrates the combinatorial logic elements used in the PDP-8. The circuit selection is limited to the inverter circuit with single or multiple inputs. These are more familiarly called NAND gates or NOR gates, depending on whether one uses positive and/or negative logic-level definitions.

### Conclusion

We could continue to discuss the behavior of the transistor as it is used in these switching-circuit primitives but will leave that to books on semiconductor electronics and physics. It is hoped that the student has gained a grasp of how to think about the hierarchical decomposition of computers into particular levels of analysis (and synthesis).

## APPENDIX 1 DEC PDP-8 ISP DESCRIPTION

|                                                                   |                                                                | Appendix 1                                                                                     |  |

|-------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

|                                                                   | DEC PDF                                                        | 2~8 ISP Description                                                                            |  |

| Pc State                                                          |                                                                |                                                                                                |  |

| AC<0:11>                                                          |                                                                | Accumulator                                                                                    |  |

| L                                                                 |                                                                | Link bit/AC extension for overflow and carry                                                   |  |

| PC<0:11>                                                          |                                                                | Program Counter                                                                                |  |

| Run                                                               |                                                                | 1 when Pc is interpreting instructions or "running"                                            |  |

| Interrupt_state                                                   |                                                                | 1 when Pc can be interrupted; under programmed control                                         |  |

| ا0_pulse_l; ا0_pulse_                                             | 2; 10_pulse_4                                                  | IO pulses to IO devices                                                                        |  |

| Mp State                                                          | 4 1 1                                                          |                                                                                                |  |

| Extended memory is not i                                          | ncluded.                                                       |                                                                                                |  |

| M[0:7777 <sub>8</sub> ]<0:11>                                     |                                                                |                                                                                                |  |

| Ŷ                                                                 | $1 > := M[0:177_8] < 0:11 >$                                   | special array of directly addressed memory registers                                           |  |

| Auto_index[0:/]<0:                                                | 11> := Page_0[10 <sub>8</sub> :17 <sub>8</sub> ]<0:11>         | special array when addressed indirectly, is incremented by                                     |  |

| Pc Console State                                                  | nting anomina (load from many)                                 | and demonstry (actions in memory) and used in 1, 2, 3                                          |  |

| Data switches<0:11>                                               | nurnae, exumine (10aa jrom memory), a                          | nd deposit (store in memory) are not included.                                                 |  |

|                                                                   |                                                                | data entered via console                                                                       |  |

| Instruction Format                                                |                                                                |                                                                                                |  |

| instruction/i<0:11>                                               |                                                                |                                                                                                |  |

| op<0:2>                                                           | := i<0:2>                                                      | op code                                                                                        |  |

| indirect_bit/ib                                                   | := i<3>                                                        | 0, direct; 1 indirect memory reference                                                         |  |

| page_0_bit/p                                                      | := i<4>                                                        | 0 selects page 0; 1 selects this page                                                          |  |

| page_address<0:6>                                                 | := i<5:11>                                                     |                                                                                                |  |

| this_page<0:4>                                                    | := PC'<0:4>                                                    |                                                                                                |  |

| PC '<0:11>                                                        | := (PC<0:11> -1)                                               |                                                                                                |  |

| l0_select<0:5>                                                    | := i<3:8>                                                      | selects a T or Ms device                                                                       |  |

| io_pl_bit := i <ll></ll>                                          |                                                                | these 3 bits control the selective generation of $-3$ volts, 0.4 $\mu$ s pulses to I/O devices |  |

| io_p2_bit                                                         | := i<10>                                                       |                                                                                                |  |

| îo_p4_bît                                                         | := i<9>                                                        |                                                                                                |  |

| sma                                                               | := i<5>                                                        | u bit for skip on minus AC, operate 2 group                                                    |  |

| sza                                                               | := i<6>                                                        | µ bit for skip on zero AC                                                                      |  |

| snl                                                               | := i<7>                                                        | $\mu$ bit for skip on non zero Link                                                            |  |

| Effective Address Calcul                                          | ation Process                                                  |                                                                                                |  |

| z<0:11> := (                                                      |                                                                | effective                                                                                      |  |

| $-ib \rightarrow z^{ii};$                                         |                                                                |                                                                                                |  |

|                                                                   | $_{3}$ ) $\rightarrow$ (M[z''] $\leftarrow$ M[z''] + 1; next); | auto indexing                                                                                  |  |

| $ib \to M[z^{H}])$                                                | I. I. MG-113.                                                  |                                                                                                |  |

| $z' < 0:11 > := (\neg ib \rightarrow z''; ib \rightarrow M[z''])$ |                                                                |                                                                                                |  |

| -11-0-115 / 0-1                                                   |                                                                | direct address                                                                                 |  |

| z"<0:11> := (page_0_b                                             | it → O⊡page_page_page_address;                                 |                                                                                                |  |

### APPENDIX 1 DEC PDP-8 ISP DESCRIPTION (Continued)

Instruction Interpretation Process Run  $\Lambda \neg$  (Interrupt\_request  $\Lambda$  Interrupt\_state)  $\rightarrow$  ( no interrupt interpreter instruction  $\leftarrow M[PC]; PC \leftarrow PC + 1;$  next fetch instruction\_execution); execute Run  $\land$  Interrupt request  $\land$  Interrupt state  $\rightarrow$  ( interrupt interpreter  $M[0] \leftarrow PC;$  Interrupt state  $\leftarrow 0; PC \leftarrow 1$ Instruction Set and Instruction Execution Process Instruction\_execution := ( and (:= op = 0)  $\rightarrow$  (AC  $\leftarrow$  AC  $\land$  M[z]); logical and tad (:= op = 1)  $\rightarrow$  (LDAC  $\leftarrow$  LDAC + M[z]); two's complement add isz (:= op = 2)  $\rightarrow$  (M[z]  $\leftarrow$  M[z] + 1; next index and skip if zero  $(M[z'] = 0) \rightarrow (PC \leftarrow PC + 1));$ dca (:= op = 3)  $\rightarrow$  (M[z]  $\leftarrow$  AC; AC  $\leftarrow$  O); deposit and clear AC jms (:= op = 4)  $\rightarrow$  (M[z]  $\leftarrow$  PC; next PC  $\leftarrow$  z + 1); jump to subroutine jmp (:= op = 5)  $\rightarrow$  (PC  $\leftarrow$  z); jump iot (:= op = 6)  $\rightarrow$  ( u in out transfer, microprogrammed to generate up to 3 pulses to an io device addressed by IO\_select io\_pl\_bit → 10\_pulse\_1 ← 1; next io\_p2\_bit → 10\_pulse\_2 ← 1; next  $io_p4_bit \rightarrow 10_pulse_4 \leftarrow 1);$ opr (:= op = 7) → Operate\_execution the operate instruction is defined below end Instruction execution ) Operate Instruction Set The microprogrammed operate instructions: operate group l, operate group 2, and extended arithmetic are defined as a separate instruction set. Operate\_execution := ( cla (:= i < 4 > = 1)  $\rightarrow$  (AC  $\leftarrow$  0); clear AC. Common to all operate instructions.  $opr_{i}(:= i < 3 > = 0) \rightarrow ($ operate group 1 cll (:= 1 < 5 > = 1)  $\rightarrow$  (L  $\leftarrow$  0); next µ clear link cma (:= i < 6 > = 1)  $\rightarrow (AC \leftarrow AC)$ ; u complement AC cml (:= i < 7 > = 1)  $\rightarrow (L \leftarrow \neg L)$ ; next µ complement L iac (:= i < |1> = 1)  $\rightarrow (L\squareAC \leftarrow L\squareAC + 1$ ); next u increment AC ral (:= i < 8:10 > = 2)  $\rightarrow$  (LDAC  $\leftarrow$  LDAC  $\times$  2 {rotate}); u rotate left rtl (:= i<8:10> = 3)  $\rightarrow$  (LOAC  $\leftarrow$  LOAC  $\times 2^2$  {rotate}); u rotate twice left rar (:= i < 8:10 > = 4)  $\rightarrow$  (LDAC  $\leftarrow$  LDAC / 2 {rotate}); u rotate right rtr (:= i<8:10> = 5)  $\rightarrow$  (LDAC  $\leftarrow$  LDAC / 2<sup>2</sup> {rotate})); u rotate twice right opr\_2 (:= i < 3, 11 > = 10)  $\rightarrow$  ( operate group 2 skip condition  $\oplus$  (i<8> = 1)  $\rightarrow$  (PC  $\leftarrow$  PC + 1); next M AC, L skip test skip condition :=  $((sma \land (AC < 0)) \lor (sza \land (AC = 0)) \lor (snl \land L))$ osr (:= i < 9 > = 1)  $\rightarrow$  (AC  $\leftarrow$  AC  $\lor$  Data switches); u "or" switches hlt (:=  $i \leq 10 > = 1$ )  $\rightarrow$  (Run  $\leftarrow 0$ )); " halt or stop FAE (:= i<3,11> = 11) → EAF instruction execution) optional EAE description

- - - - - - - 11

## APPENDIX 1 DEC PDP-8 ISP DESCRIPTION (Continued)

| KT and KMs State<br>Each K may have any or all of the following registers. There can                             | n be up to 64 optional K's.                                              |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Input_data[0:77]<0:11>                                                                                           | 64 imput buffers                                                         |

| 0utput_data[0:77 <sub>8</sub> ]<0:11>                                                                            | 64 output buffers                                                        |

| IO_skip_flag[0:77]                                                                                               | 64 test conditions                                                       |

| <pre>I0_interrupt_request[0:77 8]</pre>                                                                          | l signifies a recuest. If interrupt_state = 1, then an interrupt occurs. |

| <pre>Interrupt_request := (</pre>                                                                                | "or" of all requests from each IO device                                 |

| <pre>max(10_interrupt_request[0:77<sub>8</sub>]))</pre>                                                          |                                                                          |

| Extended Arithmetic Element, EAE (optional)<br>Provides additional arithmetic instructions (or operators) includ | ling x, /, normalize, logical shift and arithmetic shift.                |

| EAE State                                                                                                        |                                                                          |

| MQ<0:11>                                                                                                         | Multiplier Quotient                                                      |

| sc⊲D:4>                                                                                                          | Shift Counter                                                            |

| Instruction Format and Data                                                                                      |                                                                          |

| mds<0:11>                                                                                                        | multiplier divisor shift data                                            |

| s<0:4> := mds<7:11>                                                                                              | shift count parameter                                                    |

| Instruction Set for EAE                                                                                          |                                                                          |

| EAE_instruction_execution := (next                                                                               |                                                                          |

| mqa (:= i<5>) $\rightarrow$ (AC $\leftarrow$ AC $\lor$ MQ);                                                      | MQ into AC                                                               |

| sca (:= i<6>) $\rightarrow$ (AC $\leftarrow$ AC $\lor$ SC):                                                      | SC into AC                                                               |

| mql (:= i<7>) $\rightarrow$ (MQ $\leftarrow$ AC; AC $\leftarrow$ O); next                                        | AC into MQ, clear AC                                                     |

| Note only one of nmi, shl, asr, lsr, muy, or dvi can be given a                                                  | it a time.                                                               |

| $i < 8: 10^> = 00 $ $\rightarrow ;$                                                                              | 10 operation                                                             |

| $\neg$ nmi →(mds ← M[PC]; PC ← PC + 1); ne×t                                                                     |                                                                          |

| muy (:= i<8:10> = 2) $\rightarrow$ (L $\Box$ AC $\Box$ MQ $\leftarrow$ MQ x mds; SC $\leftarrow$ 0)              | multiply                                                                 |

| dvi (:= i<8:10> = 3) $\rightarrow$ (MQ $\leftarrow$ LpACpM0/mds;                                                 | divide                                                                   |

| $L\Box AC \leftarrow L\Box AC \Box MQ \mod Mds$ ; $SC \leftarrow 0$ ):                                           |                                                                          |

| nmi (:= i<8:10> = 4) $\rightarrow$ ( AC MQ $\leftarrow$ normalize (AC MQ);                                       | normalize(AC,MQ) into SC                                                 |

| SC $\leftarrow$ normalize_exponent(ACDMQ));                                                                      |                                                                          |

| sh1 (:= i<8:10> = 5) → (L□AC□MQ ← L□AC□MQ × $2^{s+1}$ ; SC ← 0);                                                 | shift left                                                               |

| asr (:= i<8:10> = 6) → (L□AC□MQ ← L□AC□MQ / $2^{s+1}$ ; SC ← 0);                                                 | shift right                                                              |

| lsr (:= i<8:10> = 7) → (L□AC□MQ ← L□AC□MQ / $2^{s+1}$ {logical};                                                 | logical shift                                                            |

| SC ← O)                                                                                                          | end EAE instruction execution                                            |

# **Chapter 8**

# Structural Levels of the PDP-81

C. Gordon Bell / Allen Newell / Daniel P. Siewiorek

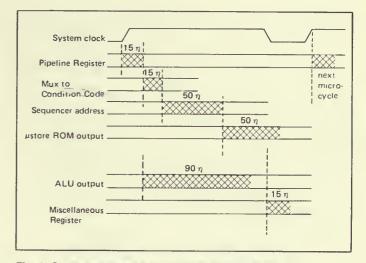

A map of the PDP-8 design hierarchy, hased on the Structural Levels View of Chap. 2, is given in Fig. 1, starting from the PMS structure, to the ISP, and down through logic design to circuit electronics. These description levels are subdivided to provide more organizational details such as registers, data operators, and functional units at the register transfer level.

The relationship of the various description levels constitutes a tree structure, where the organizationally complex computer is the top node and each descending description level represents increasing detail (or smaller component size) until the final circuit element level is reached. For simplicity, only a few of the many possible paths through the structural description tree are illustrat-

<sup>1</sup>Originally printed in C. G. Bell, J. C. Mudge, and J. E. McNamara, *Computer Engineering: A DEC View of Hardware System Design*, Digital Press, 1978, pp. 209–228. ed. For example, the path showing mechanical parts is missing. The descriptive path shown proceeds from the PDP-8 computer to the processor and from there to the arithmetic unit, or more specifically, to the Accumulator (AC) register of the arithmetic unit. Next, the logic implementing the register transfer operations and functions for the *j*th bit of the Accumulator is given, followed by the flip-flops and gates needed for this particular implementation. Finally, on the last segment of the path, there are the electronic circuits and components from which flip-flops and gates are constructed.

## **Abstract Representations**

Figure 1 also lists some of the methods used to represent the physical computer abstractly at the different description levels. As mentioned previously, only a small part of the PDP-8 description tree is represented here. The many documents which constitute the complete representation of even this small computer include logic diagrams, wiring lists, circuit schematics, printed circuit board photo etching masks, production description diagrams, production parts lists, testing specifications, programs for testing and diagnosing faults, and manuals for modification, production, maintenance, and use. As the discussion continues down the abstract description tree, the reader will observe that the tree

[X] indicates figure number of instance

Fig. 1. PDP-8 hierarchy of descriptions.

conveniently represents the constitutent objects of each level and their interconnection at the next highest level.

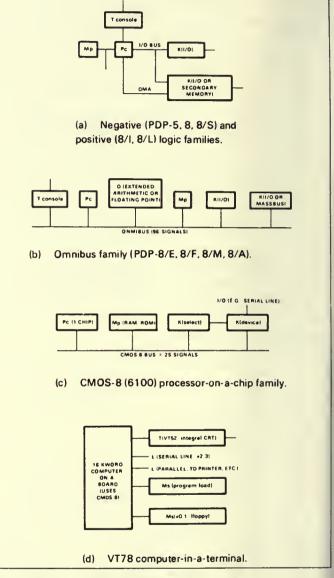

### The PMS Level

The PDP - 8 computer in PMS notation is:

C[PDP-8 technology:transistors: 12 b/w: descendants: 'PDP-8/S, 'PDP-8/I, 'PDP-8/L, '8/E, '8/F, '8/M, '8/A, 'CMOS-8; antecedents: 'PDP-5; Mp[core; #0:7; 4096 words; tc:1.5 µs/word];] Pc(Mps(2 to 4 words); instruction length: 1 2 words: address/instruction:1: operations on data:(=, +, Not, And, Minus (negate), Srr I(/2), Slr 1 (×2), +) optional operations:(×,/,normalize); data-types:word, integer, Boolean vector; operations for data access:4); P(display; <sup>1</sup>338); P(c; 'LINC); S(' I/O Bus; 1 Pc; 64K); Ms(disk, 'DECtape, magnetic tape); T(paper tape, card, analog, cathode-ray tube)

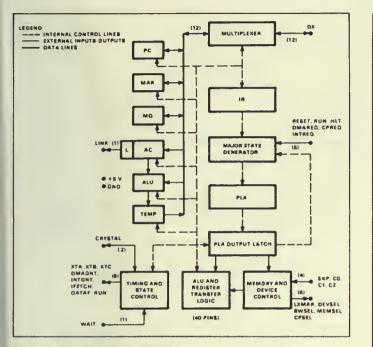

As an example of PMS structure, the LINC-8-338 is shown in Fig. 2; it consists of three processors (designated P): Pc('LINC), Pc('PDP-8), and P.display('338). The LINC processor is a very capable processor with more instructions than the PDP-8 and is available in the structure to interpret programs written for the LINC. Because of the rather limited instruction set being interpreted, one would hardly expect to find all the components present in Fig. 2 in an actual configuration.

The switches (S) between the memory and the processor allow eight primary memories (Mp) to be connected. This switch, in PMS called S('memory Bus; 8 Mp; I Pc; time-multiplexed; I.5  $\mu$ s/word), is actually a bus with a transfer rate of 1.5 microseconds per word. The switch makes the eight memory modules logically equivalent to a single 32,768-word memory module. There are two other connections (a switch and a link) to the processor excluding the console. They are the S('I/O Bus) and L('Data Break; Direct Memory Access) for interconnection with peripheral devices. Associated with each device is a switch, and the I/O Bus links all the devices. A simplified PMS diagram (Fig. 3) shows the structure and the logical-physical transformation for the I/O Bus, Memory Bus, and Direct Memory Access link. Thus, the I/O Bus is:

S(' I/O Bus duplex; time-multiplexed; I Pc; 64K; Pc controlled, K requests; t:4.5 µs/w) The I/O Bus is nearly the same for the PDP-5, 8, 8/S, 8/I, and 8/L. Hence, any controller can be used on any of the above computers provided there is an appropriate logic level converter (PDP-5, 8, and 8/S use negative polarity logic; the 8/I and 8/L, positive logic). The I/O Bus is the link to the controllers for processor-controlled data transfers. Each word transferred is designated by a processor in-out transfer (IOT) instruction. Due to the high cost of hardware in 1965, the PDP-8 I/O Bus protocol was designed to minimize the amount of hardware to interface aperipheral device. As a result, only a minimal number of control signals were defined with the largest portion of I/O control performed by software.

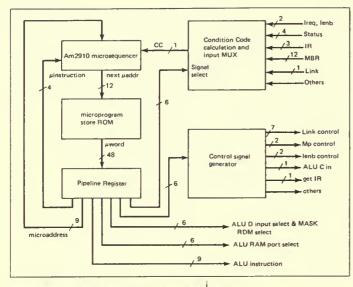

A detailed structure of the processor and memory (Fig. 4) shows the I/O Bus and Data Break connections to the registers and control in the notation used in the initial PDP-8 reference manual. This diagram is essentially a functional block diagram. The corresponding logic for a controller is given in Fig. 3 in terms of logic design elements (ANDs and ORs). The operation of the I/O Bus starts when the processor sends a control signal and sets the six I/O selection lines (IO.SELECT <0:5>) to specify a particular controller. Each controller is hardwired to respond to its unique 6-bit code. The local control, K[k], select signal is then used to form three local commands when ANDed with the three IOT command lines from the processor. These command lines are called IO.PULSE.1, IO.PULSE.2, and IO.PULSE.4. Twelve data bits are transmitted either to or from the processor, indirectly under the controller's control. This is accomplished by using the AND/OR gates in the controller for data input to the processor, and the AND gate for data input to the controller. A single skip input is used so that the processor can test a status bit in the controller. A controller communicates back to the processor via the interrupt request line. Any controller wanting attention simply ORs its request signal into the interrupt request signal. Normally, the controller signal causing an interrupt is also connected to the skip input, and skip instructions are used in the software polling that determines the specific interrupting device.

The Data Break input for Direct Memory Access provides a direct access path for a processor or a controller to memory via the processor. The number of access ports to memory can be expanded to eight by using the DMOI Data Multiplexer, a switch. The DM01 port is requested from a processor (e.g., LINC or Model 338 Display Processor) or a controller (e.g., magnetic tape). A processor or controller supplies a memory address, a read or write access request, and then accepts or supplies data for the accessed word. In the configuration (Fig. 1), Pc['LINC] and P['338] are connected to the multiplexer and make requests to memory for both their instructions and data in the same way as the PDP-8 processor. The global control of these processor programs is via the processor over the I/O Bus. The processor issues start and stop commands, initializes their state, and examines their

Fig. 2. LINC-8-338 PMS diagram.

Fig. 3. PDP-8 S('I/O Bus) iogic and PMS diagrams.

final state when a program in the other processor halts or requires assistance.

When a controller is connected to the Data Break or to the DM01 Data Multiplexer, it only accesses memory for data. The most complex function these controllers carry out is the transfer of a complete block of data between the memory and a high speed transducer or a secondary memory (e.g., DECtape or disk). A special mode, the Three Cycle Data Break, allows a controller to request the next word from a block in memory.

The DECtape was derived from M.1.T.'s Lincoln Laboratory LINCtape unit. Data were explicitly addressed by blocks (variable but by convention 128 words). Thus, information in a block could be replaced or rewritten at random. This operation was unlike the early standard IBM format magnetic tape in which data could be appended only to the end of a file.

### **Programming Level (ISP)**

The ISP of the PDP-8 processor is probably the simplest for a general purpose stored program computer. It operates on 12-bit words, 12-bit integers, and 12-bit Boolean vectors. It has only a few data operators, namely, =, +, minus (negative of), not, and slr 1 (rotate bits left), srr 1 (rotate bits right), (optional)  $\times$ , /, and normalize. However, there are microcoded instructions, which allow compound instructions to be formed in a single instruction.

The ISP of the basic PDP-8 is presented in Appendix 1. The 2<sup>12</sup>-word memory (declared MP[0:4095]<0:11>) is divided into 32 fixed-length pages of 128 words each (not shown in the ISPS description). Address calculation is based on references to the first page, page.zero, or to the current page of the Program Counter (PC\Program.Counter). The effective address calculation procedure, called MA in Appendix 1, provides for both direct and indirect reference to either the current page or the first page. This scheme allows a 7-bit address to specify a local page address.

A 2<sup>15</sup>-word memory is available on the PDP-8, but addressing more than 2<sup>12</sup> words is comparatively inefficient. In the extended range, two 3-bit registers, the Program Field and Data Field registers, select which of the eight 2<sup>12</sup>-word blocks are being actively addressed as program and data. These are not given in the ISPS description.

There is an array of eight 12-bit registers, called the auto.index registers, which resides in page.zero. This array (auto.index [0:7]<0:11>:=MP[#10: #17]<0:11>) possesses a useful property: whenever an indirect reference is made to it, a 1 is first added to its contents. (That is, there is a side effect to referencing.) Thus, address integers in the register can select the next member of a vector or string for accessing.

The processor state is minimal, consisting of a 12-bit accumulator (AC\Accumulator<0:11>), an accumulator extension bit called the Link (L\Link), the 12-bit Program Counter, the GO flip-flop,

Fig. 4. PDP-8 processor block diagram.

and the INTERRUPT. ENABLE bit. The external processor state is composed of console switches and an interrupt request.

The instruction format can also be presented as a decoding diagram or tree (Fig. 5). Here, each block represents an encoding of bits in the instruction word. A decoding diagram allows one more descriptive dimension than the conventional, linear ISPS description, revealing the assignment of hits to the instruction. Figure 5 still requires ISPS descriptions for the memory, the processor state, the effective address calculation, the instruction interpreter, and the execution for each instruction. Diagrams such as Fig. 5 are useful in the ISP design to determine which instruction operation codes are to be assigned to names and operations, and which instructions are free to be assigned (or encoded).

There are eight basic instructions encoded by 3 opcode bits of

the instruction.register, that is, IR<0:2>. Each of the first memory reference six instructions, where the opcode is less than or equal to 5, has four addressing modes (direct page.zero, direct current.page, indirect page.zero, and indirect current.page). The first six instructions in the following four categories are:

- 1 Data transmission "deposit and clear Accumulator" (DCA). (Note that the add instruction, TAD, is used for both data transmission and arithmetic.)

- 2 Binary arithmetic "two's complement add to the Accumulator" (TAD).

- 3 Binary Boolean "and to the Accumulator" (AND).

Fig. 5. PDP-8 instruction decoding diagram.

4 Program control "jump/set Program Counter" (JMP); "jump to subroutine" (IMS): "index memory and skip if results are zero" (ISZ).

The subroutine calling instruction, JMS, provides a method for transferring a link to the beginning (or head) of the subroutine. In this way arguments can be accessed indirectly, and a return is executed by a "jump indirect" instruction to the location storing the returned address. This straightforward subroutine call mechanism, although inexpensive to implement, requires reentrant and recursive subroutine calls to be interpreted by software rather than by hardware. A stack for subroutine linkage, as in the PDP-11, would allow the use of read-only memory program segments consisting of pure code. This scheme was adopted in the CMOS-8.

The "in-out transfer" instruction, opcode 6, IOT uses the remaining nine bits of the instruction to specify instructions to input/output devices. The six io.select bits select 1 of 64 devices. Three conditional pulse commands to the selected device, io.pulse.1, io.pulse.2, and io.pulse.4, are controlled by the IOT, io.control<0:2> operation code bits. The instructions to a typical I/O device are:

- 1 Testing a Boolean Condition of an IO device. 1F io.pulse.1 $\Rightarrow$ (IF io.skip.flag[io.select] $\Rightarrow$ PC = PC + 1)

- 2 Output data to a device from Accumulator. IF io.pulse.4⇒ (output.register[io.select] = AC)

- 3 Input data from a device to Accumulator. 1F io.pulse.2⇒ (AC = input.register[io.select])

There are three microcoded instruction groups selected by (IR<0:2> eqv #7), called the operate instructions. The instruction decoding diagram (Fig. 5) and the ISP description show the microinstructions which can be combined in a single instruction. These instructions are: operate group 1 ((IR<0:2> eqv #7) and not ib) for operating on the processor state; operate group 2 ((IR<0:2> eqv #7) and NOT ib<> and MB<11>) for testing the processor state; and the Extended Arithmetic Element group (not included in the ISP description) (IR<0:2> eqv #7 and ib<> and MB<11>) for multiply, divide, etc. Within each instruction the remaining bits, <4:10> or <4:11>, are extended instruction (or opcode) bits: that is, the bits are microcoded to select additional instructions. In this way, an instruction is actually programmed (or microcoded, as it was originally named before "microprogramming" was used extensively). For example, the instruction, "set

link to 1," is formed by coding the two microinstructions, "clear link" following by "complement link."

If (IR < 0:2> eqv #7) and  $(group eqv 0)) \Rightarrow$ If MB<5>  $\Rightarrow$  L = 0; next If MB<7>  $\Rightarrow$  L = not L)

Thus, in operate group 1, the instructions "clear link, complement link, and set link" are formed by coding MB < 5,7 > = 10,01, and 11, respectively. The operate group 2 instructions are used for testing the condition of the processor state. These instructions use bits 5, 6, and 8 to code tests for the Accumulator. The AC skip conditions are coded as never, always, AC eql 0, AC neg 0, AC lss 0, AC leq 0, AC geq 0 and AC gtr 0. The optional Extended Arithmetic Element (EAE) includes additional Multiplier Quo-

Table 1 PDP-8 Register Transfer Control Signals and Data Break Interface

| AC/Accumulator, L/Link and combined        | L, AC LAC      |           |  |  |  |

|--------------------------------------------|----------------|-----------|--|--|--|

| AC = 0; AC = #7777; AC = not AC;           | LAC = LAC + 1  |           |  |  |  |

| L = 0; L = 1; L = not L;                   |                |           |  |  |  |

| LAC = LAC srr 1; LAC = LAC srr 2;          | Irotates right |           |  |  |  |

| LAC = LAC sir 1; LAC = LAC sir 2;          |                |           |  |  |  |

| AC = AC or SWITCHES; AC = AC a             |                | BUS       |  |  |  |

| AC = AC xor MB; LAC = carry (AC.)          |                |           |  |  |  |

| (note that previous two commands I         | orm: LAC = AC  | + MB).    |  |  |  |

| MB/Memory.Buffer                           |                |           |  |  |  |

| MB = MB + 1;                               | Increment      |           |  |  |  |

| MB = PC; MB = AC; MB = M[MA];              | MB = DB.DATA.  | !Set      |  |  |  |

| MB= <b>0</b> ;                             |                |           |  |  |  |

| MA/Memory.Address                          |                |           |  |  |  |

| MA<0:4> = 0; MA = PC; MA = MB;             | MA<5:11> = N   | IA<5:11>; |  |  |  |

| MA = DB.ADDRESS.                           |                |           |  |  |  |

| PC/Program.Counter                         |                |           |  |  |  |

| PC = 0; PC < 0:4 > = 0;                    | !Clear         |           |  |  |  |

| PC = MB; PC<5:11> = MB<5:11>               | !Set           |           |  |  |  |

| PC = PC + 1                                | Increment      |           |  |  |  |

| IR/Instruction.Register                    |                |           |  |  |  |

| IR = 0;                                    | !Clear         |           |  |  |  |

| IR = M[MA] < 0:2 >                         | !Load          |           |  |  |  |

| M/Memory[0:4095]<0:11>                     |                |           |  |  |  |

| M[MA] = MB                                 | !write         |           |  |  |  |

| MB = M[MA]                                 | !read          |           |  |  |  |

| DB/DATA.BREAK interface                    |                |           |  |  |  |

| DB.DATA<0:11> I Input to MB                |                |           |  |  |  |

| DB.ADDRESS<0:11> ! Input to MA             |                |           |  |  |  |

| MB<0:11>                                   |                |           |  |  |  |

| DB.REQUEST ! Control inputs to Pc          |                |           |  |  |  |

| DB.DIRECTION                               |                |           |  |  |  |

| DB.CYCLE.SELECT<0:11>                      |                |           |  |  |  |

| ADDRESS.ACCEPTED ! Control outputs from Pc |                |           |  |  |  |

| WORD.COUNT.OK                              |                |           |  |  |  |

| BREAK.STATE                                |                |           |  |  |  |

---- CONTROL SIGNALS

Fig. 6. PDP-8 register transfer level PMS dlagram.

tient (MQ) and Shift Counter (SC) registers and provides the hardwired operations, "multiply," "divide," "logical shift left," "arithmetic shift," and "normalize." If all the nonredundant and useful variations in the two operate groups were available as separate instructions in the manner of the first seven (DCA, TAD, etc.), there would be approximately 7 + 12 (group 1) + 10 (group 2) + 6 (EAE) = 35 instructions in the PDP-8.

## The Interrupt Scheme

External conditions in the input/output devices can request that the processor be interrupted. Interrupts are allowed if the processor's interrupt enable flip-flop is set (if INTERRUPT. ENABLE eqv 1). A request to interrupt (i.e., INTERRUPT. REQUEST = 1) clears the interrupt enable bit (INTERRUPT. ENABLE = 0), and the processor behaves as though a "jump to subroutine" 0 instruction (JMS 0) has been executed. A special IOT instruction (MB<0:11> eql #6001) followed by a "jump to subroutine indirect" to 0, and instruction (MB<0:11> eql #5220) returns to the processor to the interruptable state with INTER-RUPT.ENABLE a 1. The program time to save the processor state is six memory accesses (9 microseconds), and the time to restore the state is nine memory accesses (13.5 microseconds).

Only one interrupt level is provided in the hardware. If multiple priority levels are desired, programmed polling is required. Most I/O devices have to interrupt because they do not have a program-controlled device interrupt-enable switch. For multiple devices, approximately three cycles (4.5 microseconds) are required to poll each interrupter.

## **Register Transfer Level**

More detail is required than is provided by either the PMS or ISP levels to describe the internal structure and behavior of the processor and memory. Figure 4 shows the registers and controllers at a block diagram level, and Fig. 6 gives a more detailed version using PMS notation. Table 1 gives the permissible register transfer operations that the processor's sequential control circuit can give to the PDP-8 registers.

Although electrical pulse voltages and polarities are not shown in Table 1, the operations are presented in considerably more detail than shown in Fig. 4. As Fig. 6 shows, the registers in the processor cannot be uniquely assigned to a single function. In a minimal machine such as the PDP-8, functional separation is not economical. Thus, there are not completely distinct registers and transfer paths for memory, arithmetic, program, and instruction flow. (This sharing complicates understanding of the machine.) However, Fig. 6 clarifies the structure considerably by defining all the registers in the processor (including temporaries and controls). For example, the Memory Buffer (MB\Memory.Buffer<0:11>)

Fig. 7. PDP-8 Pc state diagram.

is used to hold the word being read from or written to memory. The Memory Buffer also holds one of the operands for binary operations (for example, AC = AC and MB). The Memory Buffer is also used as an extension of the Instruction.Register during the instruction interpretation. The additional physical registers, not part of the ISP, are:

MB\Mempry.Buffer<0:11>

Holds memory data, instruction, and operands.

MA\Memory.Address<0:11>

Holds address of word in memory being accessed. IR\Instruction.Register<0:2>

Holds the value of current instruction being performed. state.register<0:1>

A ternary state register holding the major state of memory cycle being performed—declared as 2 bits.

F\Fetch:=(IF state.register eqv 0)

Memory cycle to fetch instruction.

- D\Deferred:=(IF state.register eqv 1)

- Memory cycle to get address of operand.

- E\Execute:=(IF state.register eqv 2)

Memory cycle to fetch (store) operand and execute the instruction.

Fig. 7. (Continued)

The emphasis in Fig. 6 is on the static definition (or declaration) of the information paths, the operations, and state. The ISP interpretation (Appendix I) is the specification for the machine's behavior as seen by a program.

As the temporary hardware registers are added, a more detailed ISPS definition must be given in terms of time and in terms of temporary and control registers. Instead, a state of diagram (Fig. 7) is given to define the actual processor which is constrained by both the ISP registers, the temporary registers implied by the implementation, and time. The relationship among the state diagram, the ISP description, and the logic is shown in the hierarchy of Fig. I. In the relationships shown in the figures, one can observe that the ISP definition does not have all the necessary detail for fully defining a physical processor. The physical processor is constrained by actual hardware logic and lower level details even at the circuit level. For example, a core memory is read by a destructive process and requires a temporary register (MB) to hold the value being rewritten. This is not represented within a single ISPS language statement because ISPS defines only the nondestructive transfer; however, it can be considered as the two parallel operations MB = MP[MA]; MP[MA] = 0. The explanation of the physical machine, including the rewriting of core using ISPS, is somewhat more tedious than the highest level description shown in Appendix I. For this reason, the state diagram is used (Fig. 7), and the description of the physical machine (in ISPS) is left as an exercise for the reader.