# Section 1

# The IBM 701-7094 II sequence, a family by evolution

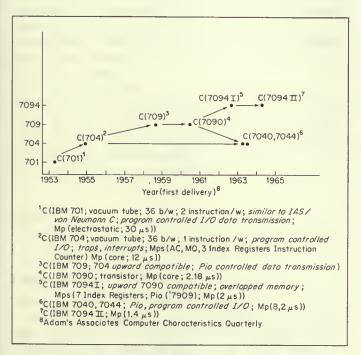

The IBM 701, 704, 709, 7090, 7040, 7044, 7094 I, and 7094 II sequence relationship is shown in Fig. 1. The group is not a compatible series. The IBM 701 [Astrahan and Rochester, 1952; Buchholz, 1953] is a forerunner of the series; all except the 701 are painfully compatible. The sequence is included because the 7090 is a reference or benchmark of scientific-computer power. All machines use 36-bit words. The 701 stores two instructions/word in the same manner as the IAS computer (Chap. 4), whereas all others in the sequence store only one instruction/word. The 701, 704, and 709 are first-generation, vacuum-tube technology; the rest are second-generation.

The IBM 7094 II description given in Chap. 41 is based directly on information in the Programming Reference Manual, but the Appendices of that chapter give the ISP of the Pc, a Pio, and a K as inferred by the authors of this book. The description of the Pc gives the instructions in the 704 and 7044

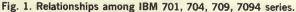

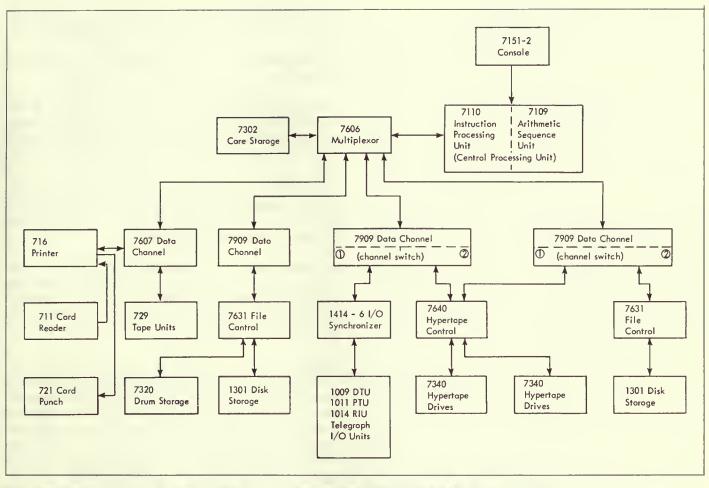

#### Fig. 2. IBM 701 PMS diagram.

to show an evolution. However, the major evolutionary change does not appear in Pc's ISP but in the PMS structure.

The 704 structure, like that of the 701 (Fig. 2), provides only for peripheral transfers to primary memory via Pc under programmed control with no interrupt system. As such, only one T or Ms could operate easily at a time. The 709 introduced the Pio('Data Channels) to improve the ability to transfer data between Mp and Ms without requiring Pc intervention. Concurrent operation of several I/O devices is carried out by multiple Pio's along the lines of the 7094 II PMS structure (Fig. 1, Chap. 41, page 518). However, the utilization of the data channels tends to be rather low, particularly when the data channel is controlling very slow devices (e.g., card equipment and line printers). When operating a high-speed tape unit at 90,000 × 6 bits/sec the utilization of the data channel is still only approximately 3 percent. A program interrupt method of data transfers would have been sufficient.

The incompatibility among the machines, especially the 7090-7040-7094, is disheartening, both from the point of view of a user and an engineer. The incremental hardware needed

to achieve compatibility is inexpensive when the system price is considered. Also, the incremental changes in the ISP do little to increase the Pc performance. Compared with the 704, the extensive order code of the 7094 shows an evolution in which for marketing, emotional, or analytic reasons new instructions were added. The index registers and their instructions are a good example of this trend. The 7094 has a very general set of index-register transmission instructions; if implemented properly, they are probably easier to provide than the original 704 instructions.

In the implementation of the double-precision floating-point hardware, the sense-indicator register is needed for temporary

storage. Thus a user has to preserve this register when doubleprecision floating-point instructions are given. The reason for this undoubtedly relates to field modifications and cost. In an original design this would be inexcusable; in this case doubleprecision floating point is undoubtedly worth the loss of sense indicators.

All in all, the designers of the 704-7094 II provided increased generality through evolution. They gradually ran out of patching time, technology, instruction encoding space, and memory addressing bits, while exceeding compatibility constraints. It was indeed time to create the IBM System/360.

# Chapter 41

# The IBM 7094 I, II

### Introduction

The IBM 7094 I and 7094 II computers are the last of a series of computers beginning with the IBM 704 (Fig. I, page 515). The series is an outgrowth of the IBM 701. Although the series is designed for scientific (arithmetic) calculations, its speed and structure allow it to be used for general-purpose computation. Business-type processing which uses string data is efficiently handled by conversion into fixed-length fields at input and output. From about 1956 to 1966 the family was the standard of large computers in the United States, there being approximately 20 701, 50 704, 20 709, 50 7090, 130 7094 I, 125 7094 II, 120 7040, and 120 7044 computers in existence.

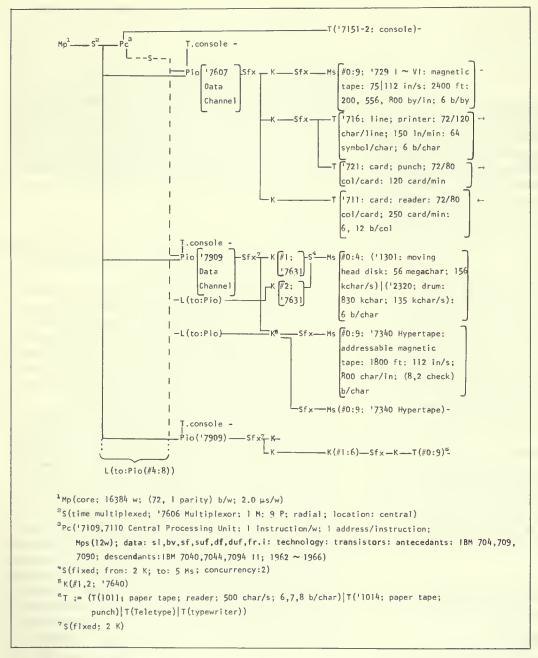

The PMS structure is a single central processor (Pc) with multiple input/output processors (Pio's) (for all except the 701 and 704). The Pio's provide for multiple transfers to primary memory (Mp) at high information flow rates. The structure allows for duplex connection to terminal (T) or secondary-memory (Ms) control (K). This provision permits the system to be used in realtime applications requiring significant computation, high-data-rate transfers with other systems, and high availability. However, the system was not initially designed for time sharing and multiprogramming use, and the attempt to so use it required modification [Corbato et al., 1962].

The word length is 36 bits. There is one single-address instruction/word. In all but the 7094 the processor interprets instructions serially. In the 7094 one register instruction look-ahead is used. The Pc has index registers, the 704 being the first IBM computer to use them. Their number increased from three in the 704  $\sim$  7090 to seven in the 7094, as their usefulness became apparent.

#### Structure

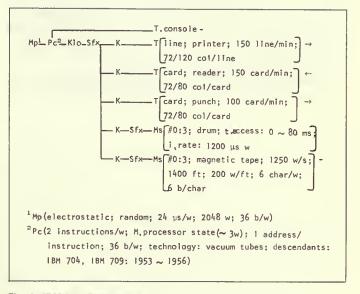

A simple tree-structured IBM 7094 I using PMS is shown in Fig. I and using a conventional block diagram in Fig. 2.

## Primary memory (Mp) and P-Mp switch

The primary memory, Mp('7302 Core Storage), has a capacity of 32,768 36-bit words with a cycle time of 2 microseconds. The actual memory has a 72 + 1 parity bit word for even and odd addresses of 36-bit words. A request for two 36-bit words can be

acknowledged in one 2-microsecond memory cycle. Thus Mp is Mp('7302 Core Storage;  $2 \mu s/w$ ; 16384 w; (72, I parity) b/w) for the 7094 I, and Mp(I.4 $\mu s/w$ ; 16384 w; (72, I parity) b/w) for the 7094 II.

The S('7606 Multiplexor; time multiplexed) provides access to Mp from any one of nine P's. Only Pc can request two 36-bit words at a time from Mp for instruction look-ahead and double-word operations. There can be only one Pc in the system.

## Processors, P

Three processors are described: Pc('7109, 7110 Central Processing Unit/CPU), Pio('7607 Data Channel), and Pio('7909 Data Channel).

All P's behave similarly in that Pc instructions and Pio commands<sup>1</sup> are fetched (or requested) from Mp and then interpreted in P. An instruction location counter in P addresses the next instruction. A processor instruction may, in turn, require the processor to access Mp for data, to perform transfers, to modify its state, etc. Although structurally the P's are similar, organizationally the Pc is superior to the Pio('Data Channel)'s; Pc issues programs to Pio's and start and stops (controls) Pio's.

Two-way communication is required between Pc and the Pio's. Tasks (jobs or programs) for Pio's are first set up in Mp by Pc. Pc then demands that Pio execute the program independently under its own control. Initialization takes place when Pc sets the instruction counter of a Pio. Upon task completion in Pio, an interrupt request is sent to Pc from Pio.

Below we first give a description of the Pc. Then the Pio('7909) is presented in detail and the Pio('7607) is outlined. The reader should compare the two Pio's. The Pio('7909) is a later design than the Pio('7607). It interprets instructions for the block of data being transferred and issues instructions to the KMs or KT. The earlier Pio('7607) interprets the instructions for controlling the information being transferred; the Pc interprets and issues the instructions to KMs or KT. The 7909 is therefore able to control more closely a T or Ms using a single program without need for Pc intervention.

<sup>&</sup>lt;sup>1</sup>IBM attempts to distinguish between Pc and Pio's terminologically by "instruction" and "command." We make no such distinction in the following discussion; P's interpret instructions.

Fig. 1. IBM 7094 | PMS diagram.

Fig. 2. IBM 7094 data-processing system configuration. (Courtesy of International Business Machines Corporation.)

## Central processing unit, Pc

The Pc has three physical parts: the T('7151-2 Console), the D('7110 Instruction Processing Unit), and the K('7109 Arithmetic Sequence Unit). In terms of gross PMS parameters the 7094 I can be described similar to footnote three of Fig. 1 as

- Pc 7109, 7110, 7151-2 Central Processing Unit/CPU; 36 b/w; 1 address; 1 instruction/w; data: (si, bv, sf, suf, df, duf, fr.i); number representation: sign, magnitude; Mps('Accumulator 'Multiplier Quotient 'Index Bes

- Mps('Accumulator, 'Multiplier\_Quotient, 'Index\_Registers [1:7], 'Sense\_Indicators, 'Instruction\_Counter, 'Trap\_Enable(1:12), 'miscellaneous\_bits(1:7))

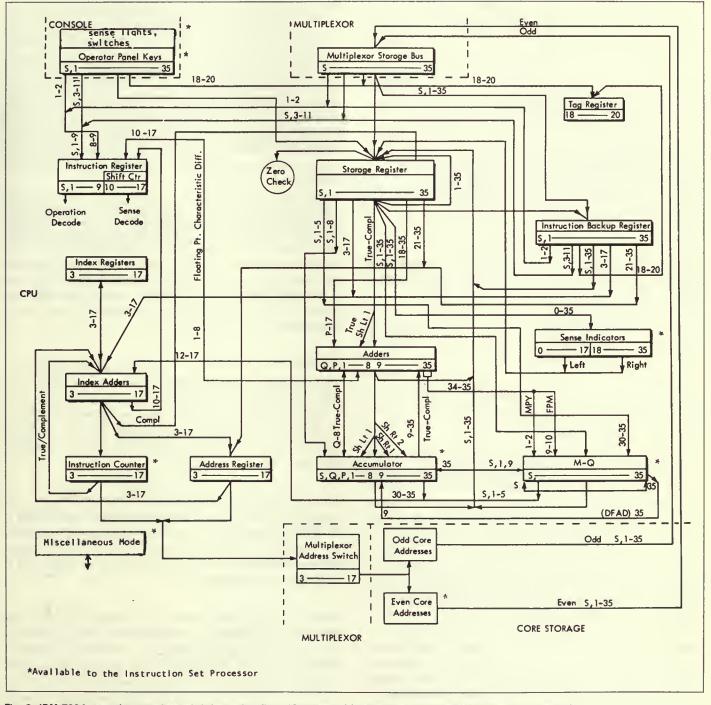

The Pc will be discussed in two parts: the Register-transfer level implementation and the Instruction-set Processor. These are partially redundant, but they offer another opportunity to compare the two types of descriptions. The Pc hardware will be described by first giving the registers and the interregister transfer paths. Then the process by which instructions are interpreted will be described. (Interpretation occurs in a distinct set of memory cycles, called instruction/I, execute/E, logic/L, and buffer/B, which are sometimes mentioned in describing registers and will be fully discussed later.)

#### Processor registers and mode bits registers

Figure 3 gives the Pc registers and the data transfer paths. Both the ISP registers (denoted by °) and the temporary registers are given. The ISP registers and modes are controlled by the program.

Instruction counter  $(IC)^{\circ}$ . The Instruction Counter, IC, is 15 bits. It is used by the processor to locate the next instruction in Mp. Once the program is started, the IC can be set to an address specified by a transfer instruction. For most instructions, the IC is stepped sequentially by I with each new instruction. The IC is normally advanced at the end of each instruction (I cycle).

Instruction backup register (IBR). The Instruction Backup Register, IBR, is a 36-bit register,  $\langle S, 1:35 \rangle$ , and is used to buffer the next instruction. Pc attempts to have the next instruction available in IBR, since the Mp permits 72-bit transfers, thus avoiding an unnecessary reference to Mp. When the instruction reference is to an even location, the IBR is loaded with the contents of the next higher odd address after the contents of the even address have been placed in the Storage Register. The IBR is also used for fetching operands in double-precision operations.

Address register (AR). The Address Register, AR, is 15 bits and receives information from the Storage Register, Instruction Backup Register (at the beginning of a storage reference I or E cycle), Index Register, and Index Adder. The contents of the AR are sent to the Multiplexor Address Switch to select the core memory location.

Instruction register (IR). The 18-bit Instruction Register, IR, is divided into two parts: bits  $\langle S, 1:9 \rangle$  always contain the operation part of the instruction, and bits  $\langle 10:17 \rangle$  form the Shift-counter Register. The Shift Counter is used during shifting, multiplication, division, and floating-point instructions. Bits  $\langle 10:17 \rangle$  may also contain a sense instruction address, operation codes for those instructions which require an address part, and the class and unit codes for input/output instructions.

Storage register (SR). The 36-bit Storage Register, SR, stores information that comes from or goes to core storage.

Adders (not a register). The Adders furnish a 36-bit path for data going from the storage register to other registers in the processor.

Accumulator register  $(AC)^{\circ}$ . The Accumulator Register, AC, is 38 bits (a 35-bit word with a 1-bit sign, and 2 bits for overflow

conditions, P and Q). The AC is used to hold one factor during arithmetic or logical operations and to receive results from the adders.

Information may be shifted into the accumulator from the MQ, 1 bit at a time.

Multiplier-quotient register  $(MQ)^{\circ}$ . The MQ Register is 36 bits. During a multiply instruction, MQ contains the multiplier; during a divide instruction, MQ receives the quotient. It can be shifted right or left, independently, or combined with AC into a 72-bit register.

Sense indicator register  $(SI)^{\circ}$ . The Sense Indicator Register, SI, is 36 bits. SI is normally used as a set of binary program switches which can be set and tested. However, it is also used as a temporary register in double-precision arithmetic operations.

Index registers  $(XR)^\circ$ . Seven 15-bit Index Registers, XRs, in the 7094 system are used for address modification. They are specified by the tag bits of an instruction (bits  $\langle 18:20 \rangle$ ) and modify an address by adding the two's complement of their contents to the address. In the earlier 7090 (and 7044) only XR[1, 2, 4] are available.

Multiple tag mode<sup>•</sup>. In Multiple Tag Mode only Index Registers I, 2, and 4 can be specified. The indexing function specified is determined by the "logical-or" of each index register specified. When not in Multiple Tag Mode, each 3-bit number selects one of seven index registers. The 1-bit Multiple-Tag-Mode Register maintains the state of the mode. The requirement for the two modes comes entirely from the need to maintain compatibility between the 704, 709, 7090, 7040, and 7044 (which have three index registers addressed as in Multiple Tag Mode) and the 7094 I and 7094 II which have seven index registers.

Tag register (TR). This temporary register holds the tag field of the instruction being executed and is used to select the Index Register being addressed.

Index adders (XAD) (not a register). A separate 15-position Index Adder is used for the Index-register operations. All storing, loading, changing, and modifying of Index Registers is via the Index Adders.

Accumulator overflow<sup>°</sup>. The Accumulator Overflow Indicator is turned on whenever a I passes into or through position P from position 1 of the AC as a result of the execution of a fixed-point arithmetic or a shifting instruction.

Fig. 3. IBM 7094 central-processing-unit information flow. (Courtesy of International Business Machines Corporation.)

*Divide-check*<sup>°</sup>. The Divide-Check Indicator is turned on, in fixedpoint or floating-point division, if the magnitude of the number in the AC (dividend) is greater than or equal to the magnitude of the number in memory (divisor).

*Input-output check*<sup>•</sup>. The Input-Output Check Indicator (I-O check) is turned on by the attempted execution of an input/output instruction without first selecting an input/output unit.

Transfer trap mode<sup>•</sup>. The computer can be operated in a special Transfer Trap Mode. Operation in the Trap Mode permits the program to run at normal speed with interruptions of normal operation only at transfer points. At such points the location of the last sequential instruction is saved, and a transfer of control is made to a fixed location.

Sense switches<sup>°</sup>. Six Sense Switches are located on the console. They may be turned on or off manually, and there are instructions which sense them.

Sense lights<sup>\*</sup>. Four Sense Lights are also on the console. Any one of these lights may be turned on, off, or the status tested by instructions.

*Panel in-out switches*°. These 36 switches on the console may be read by an instruction.

#### Instruction-set interpretation

The basic computer clock cycle is 2.0  $\mu$ s in 7094 I and 1.4  $\mu$ s in 7094 II, as dictated by Mp. Within the single 2- (or I.4-) microsecond cycle, up to 10 sequential register transfers and/or data operations can take place, each of which transfers information among the Pc's registers; several operations may occur simultaneously. In Pc four different cycles are used: instruction/I, execute/E, logic/L, and buffer/B. The cyclic sequence of an instruction is fixed, always beginning with an I cycle and progressing to E, L, or B cycles, depending on the instruction. The number of cycles required for an instruction may vary from I (e.g., transfer) to I9 (e.g., double-precision floating-point divide).

Instruction cycle (I). The I cycle begins when IC furnishes the instruction location to Mp, via S('Multiplexor). The addressed instruction word taken from Mp goes to the Multiplexor Storage Bus (Fig. 3). From the Multiplexor Storage Bus the instruction is read into the Storage Register where it is separated into the operation portion and the address portion of the instruction word.

The operation portion of the Storage Register goes into the Instruction Register, where the operation code is decoded and the execute control circuitry is set up to perform the operation specified by the instruction. The address portion of the instruction word, now located in the Storage Register, may be used directly. Normally, however, it goes to the Address Register and then to the Multiplexor Address Switch to locate the appropriate data word in Mp. If the address is to be modified, it is routed from the Storage Register to the Index Adders for Index-register modification. The modified address is then brought to the Address Register and on to the Multiplexor Address Switch to locate the data word in core storage.

Concurrently, during the same instruction cycle, a second instruction, located at the immediately higher odd-numbered Mp address location, is bronght to the Instruction Backup Register/ IBR. While in the IBR, the odd-numbered instruction is partially decoded to determine if it meets certain criteria for concurrent execution, thus saving a second Mp reference. If the instruction in the IBR cannot be executed with the current instruction, it is ignored in the current I cycle and is brought into the Storage Register on the next I cycle.

*Execution cycle* (E). The execution (E) cycle is used when a reference to core storage is needed. All instructions requiring an operand have an E cycle following the I cycle.

Indirect addressing of an instruction requires an extra E cycle. In other words, an instruction that normally goes from I to E to be executed will go to I, E, and again to E if it is indirectly addressed.

Logic cycle (L). The L cycle is an execute cycle that does not require a reference to Mp. Many instructions use both E and L cycles when information is required from storage and the instruction cannot be completed during an E cycle. Other instructions require no reference to storage and, therefore, use only I and L cycles for their completion.

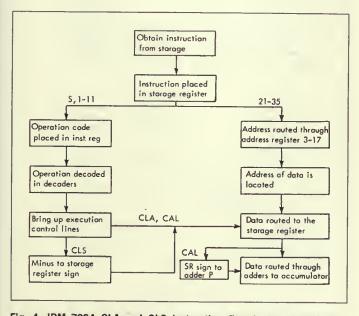

Buffer cycle (B). A buffer (B) cycle is a null Pc cycle; it is used when the data channels get information from or put information into core storage. This information can be either data or datachannel commands. All demands for B cycles come from the channels themselves. Because of the nature of Ms's and T's, the demand for a B cycle takes precedence over an instruction being performed by Pc. If Pc is in its logic cycle, then both an L and B cycle occur simultaneously. Instruction interpretation. Instruction flow diagrams for the CLA, CAL, and CLS instructions are given in Fig. 4. These diagrams show the sequential process of instruction execution. Although the flow diagrams for these instructions are trivial, the general process is still apparent. The more complex instructions, for example, double-precision floating-point divide, are carried out in a similar fashion, but with many more operations. The registers, transfer paths, and interregister data operations are the register-transfer-level primitives from which the ISP is implemented. The data flow diagram (Fig. 3) explicitly defines the main registers and register operations within Pc.

#### Pc ISP

The Pc Instruction-set Processor is given in Appendix I of this chapter. The instructions are arranged in groups according to the location of operands. These groups are:

Operations on Mp $Mp \leftarrow u Mp$ (unary operation/u on Mp) $Mp \leftarrow u Mps$ (unary operation on Mprocessor<br/>state/Mps) $Mp \leftarrow Mp b Mps$ (binary operation/b)

Fig. 4. IBM 7094 CLA and CLS instruction flowcharts. (Courtesy of International Business Machines Corporation.)

Operations on AC and MQ Mps ← u Mps Mps ← u Mp Mps ← Mps b Mp Operations on the index registers Operations on the sense indicators Instruction for program control

## Memory mapping for multiprogramming and Mp(65536 w)

A special option provides multiprogramming by allowing a program to run in a protected area of Mp. Two registers are used: The base register establishes the lower bound of the program, and the length register establishes the upper bound. Pc checks that all program references are within the protected area.

Two Mp(32678 w)'s can be used on the computer. Mp is then considered as A core and B core for addresses 0:32767 and 32768:65535. A 1-bit register is used to select whether A or B core is to be used for data; and one I-bit register is used to select whether A or B core is to be used for the instruction. These modifications were used at M.I.T. in their Compatible Time Sharing System/CTSS [Corbato et al., 1962] which used a 7094 II.

### Pio('7607 Data Channel)

The Pio('7607 Data Channel) executes programs which transfer data between Mp and Ms(magnetic tape) or T(card; reader, punch), (line; printer)). The paths and structure can be seen in Fig. 1.

Transferring blocks of data between Mp and an Ms or a T via the 7607 data channel takes places as follows:

- I Pc sets up the block transfer program in Mp for Pio.

- 2 Pc attaches a K for Ms(magnetic tape) or for T(card;reader) to Pio. (Faults in the connection may cause K to interrupt Pc.)

- 3 Pc starts the Pio by loading the Pio's instruction counter.

- 4 The data transmission takes place. On input, for example, T or Ms transmits a 6-bit character (or a 72-bit word) to K. The characters are buffered (collected) in K and sent on to Pio. Pio then requests a memory access from Mp via the S('7606 Multiplexor) and, finally, a data word is transmitted to Mp.

- 5 At the termination of a simple data block transfer, Pio fetches the next instruction from Mp. If the next instruction-task type is the same, Pio and K remain logically linked and continue to transmit data.

6 At the termination of the task, the completion signal from Pio causes Pc to interrupt and Pio may also halt.

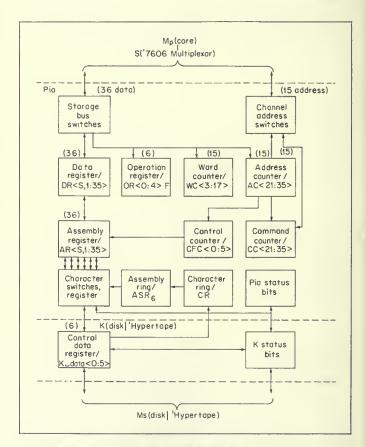

#### Pio('IBM 7909 Data Channel)

Ms('1301 Disk Storage, '7340 Hypertape Drives) and the T('Tele-Processing equipment) communicate with Mp via the Pio('7909 Data Channel). Four 7909 Data Channels may be attached to a 7094 I or II system.

K('7631 File Control) is required for M(disks). Several K('7631) can be used with the 7094 system alone or shared with an IBM 1410 system or shared with another IBM 7000 series (not 7072 system).

When Ms('7340 Hypertape Drives) are attached to the 7094 system, K('7640 Hypertape Control) is used between the 7909 data channel and the drives. One K('7640) may be attached to a 7094 system; it has two paths, each of which can be used for data transmission.

The K('1416-6 Input-Output Synchronizer) is used with T('Teleprocessing Equipment)'s. The structure for these T's is rather elaborate, yet only six T's can be active at a time.

Transferring data from Mp to a T or an Ms via the 7909 takes place as follows:

- 1 Pc sets up the data-transfer management program in Mp for a Pio.

- 2 Pc starts Pio by setting Pio's command (instruction) location counter at the origin of the task program in Mp. (Faults in the connection may cause Pio interrupts to Pc.)

- 3 Pio issues an instruction to be executed by K. This establishes a state in K which selects and initializes the particular Ms or T and attaches the peripheral device K to Pio. (Faults in this selection may cause interruption of Pio.)

- 4 The data-transmission instruction is read and initializes Pio.

- 5 The data transmission takes place under control of Pio-K. The K of the selected device assembles characters. Input characters are transferred to Pio which assembles them into words and in turn transfers them to Mp.

- 6 At the termination of a data block transfer instruction, another instruction is fetched from Mp by Pio. This instruction may be to another K.

- 7 At the termination of the Pio program, Pio signals completion by interrupting Pc.

This discussion is based on information taken from the IBM 7094 Reference Manual. The body of the description is contained

in ISP descriptions (Appendices 2, 3 and 4 of this chapter). The main registers of Pio are shown in Fig. 5. These registers are declared and their function is explained in the first section of the ISP description of Pio (Appendix 2). The remainder of the ISP description is concerned with defining the interpreter and the ISP instruction set.

There are about 50 bits in the K's (see Appendix 3). A knowledge of K's state and the K process is required for understanding the Pio. A description of the K and Pio data-transmission processes is given in Appendix 2.

The Pc instructions controlling Pio are presented in Appendix 4.

The level of detail in the appendices is slightly greater than that in normal ISP description. It is, however, not completely precise, as the behavior is extremely time- and Ms- or T-dependent. The sequence check conditions are incomplete; that is, the

Fig. 5. IBM 7909 data-channel-registers diagram.

conditions for illegal instruction sequences are not given. Both ISP and text descriptions are given for parts which are particularly complex.

The ISP description should be observed in the following sequence: Pio State; K State (Appendix 3); Pio Instruction Format; Pio Interpreter; Pio Instruction—Control (or Initialization) instructions, Block Transfer (or Copy) instructions, Conventional Move and Transfer instructions, and Interrupt Control instructions; Instructions in Pc (Appendix 4); Interrupt Operation; and Processes defining data movements between K and Pio (Appendix 2). The Pio, K, and Ms or T processes are, in several ways, more complex than those of a Pc. First, Ms or T activity is not categorized as nicely as a Pc instruction set. The T or Ms events occur at times peculiar to the device—not a simple synchronous clock. Finally, the peripheral components have a large number of error states.

## Conclusions

The series ending with the IBM 7094 II is a significant member of the computer population. It provides a good example of the evolution in computer systems that occurred from 1954 to 1965.

#### References

CorbF62; FrizC53; GreeJ57; GrumM58; RossH53; SaxoJ63; StevL52; A22-6703 IBM 7094 Principles of Operation

#### APPENDIX 1 IBM 7094 PC ISP

|                                                     | Appendix 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     | IBM 7094 Pc  SP Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| is dealand, its action is not described. Tran-Mod   | a and relocation schemes used for the 7040 and 7094. The Trap-Mods flip-<br>le allows any change of the Instruction Counter to cause a trap. The Ins<br>is used to save time in program execution. The description of the arith                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AC <q,p,s,1:35></q,p,s,1:35>                        | * Accumulator, 38 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ACs <s,1:35> := AC<s,1:35></s,1:35></s,1:35>        | * signed AC word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AC1⊲P,1:35> := AC⊲P,1:35>                           | * logical AC word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P := AC <p></p>                                     | * carry for AC $\triangleleft$ :35>; AC overflow is also set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Q := AC <q></q>                                     | * carry for bits\$P,1:35>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S := AC <s></s>                                     | * sign bit of AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MQ <s,1:35></s,1:35>                                | * Multiplier-Ouotient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ACMQ <s,q,p,1:71>:= AC CMQ&lt;1:35&gt;</s,q,p,1:71> | * double word accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| \$1<0:35>                                           | Sense Indicators or program flags must be preserved if<br>double precision floating point instructions are given                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XR'[1:7]<3:17>                                      | Index Registers in 7094                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XR''[A,B,C]<3:17> := XR[1,2,4]<3:17>                | * Index Registers for 704, 7090                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Multiple_Tag_Mode                                   | program ewitch to force compatibility with 704, 7090; o<br>3 index registers XR[A,B,C] are in 704, 7090                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10<3:17>                                            | * Instruction Location Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Run                                                 | * indicates whether machine is executing instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Divide_Check                                        | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ACLOVERFIOW                                         | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MQ_overflow                                         | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Input_Output_check                                  | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Trap, request <a:h></a:h>                           | Request to trap Pc from Pio #A#H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Trap_Mode                                           | * Allows trapping or not of transfer instructions (not described)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pc Console State                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Keys<0135>                                          | * console data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Sense_Switches<0;5>                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sense_Lights<0:3>                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Mp State                                            | A second s |

| M[0:32768-1] <s,1:35></s,1:35>                      | Primary Memory of 2 <sup>15</sup> w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Instruction Format                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| instruction <s,1:35></s,1:35>                       | corresponds to the physical Storage Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Y<21:35> := instruction<21:35>                      | generally the address part; used to calculate the effect<br>tive address; corresponds to the physical Address Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| T<18:20> := instruction<18:20>                      | the XR to use: 1,7; 0 means no indexing; correspond<br>a physical register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| F<12:13> := instruction<12:13>                      | indirect address specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| indirect := (F<12:13> = 11)                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| op<\$,111> = instruction<\$,111>                    | op code; corresponds to a physical register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

```

R<18;35> ;= instruction<18;35>

right half of instruction used to select SI bits

D<3:17> := instruction<3:17>

Decrement part of instruction, used to directly modify XR's

specifies variable length part of operation

C'<12:17> := instruction<12:17>

C<10:17> := instruction<10:17>

convert instruction parameter

c<15:17> := instruction<15:17>

specifies character position in 7040, 7044 or extends op code

Effective Address Calculation Process

e < 21:35 > := (\neg indirect \rightarrow e';

effective address calculation

indirect \rightarrow instruction \langle 18:35 \rangle \leftarrow M[e^+] \langle 18:35 \rangle; next e<sup>+</sup>)

1 level indirect addressing

e' < 21:35 > := ((T = 0) \rightarrow Y;

indexed effective

(T \neq 0) \rightarrow Y - XR[T])

e"<23:35>:= e'<23:35>

sc<28:35>:= e'<28:35>

a truncation of e, used for specifying number of shifts:

corresponds to a physical register

XR[T]<3:17> := (

index registers are or'd together in multiple tag mode

---Multiple_Tag_Mode --→ XR'[T];

Multiple_Tag_Mode → (

(T < !3 \rightarrow XR''[A]) \lor (T < !9 \rightarrow XR''[B]) \lor (T < 20 \rightarrow XR''[C])))

The description for Multiple Tag Mode is incomplete for the case of writing in several index registers at one time. The only

```

way this could be accomplished in the description would be to define each load index register instruction as microprogrammed.

Data Formats

| s1<\$,1:35>                                                                                                                                         | logical data; unsigned integer/boolean vector                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| sx<\$,1:35>                                                                                                                                         | single precision fixed point (integer) data                   |

| sx sign := sx <s></s>                                                                                                                               |                                                               |

| sx magnitude⊲:35> := sx⊲:35>                                                                                                                        |                                                               |

| sf<\$,1:35>                                                                                                                                         | single precision floating point value of: sf_signDsf_mantissa |

| sf sign := sf <s></s>                                                                                                                               | ×2 <sup>8 fuexponent</sup>                                    |

| sf exponent<1:8> := 200 <sub>8</sub> - sf<1:8>                                                                                                      |                                                               |

| sf mantlssa<0:26>:= sf<9:35>                                                                                                                        |                                                               |

| df[0:1]<\$,1:35>                                                                                                                                    | double precision floating point value of: df_signOdf_mantissa |

| df sign := df[0] <s></s>                                                                                                                            | 10                                                            |

| df exponent<1:8> := 200 <sub>8</sub> - df[0]<1:8>                                                                                                   | $\times 2^{df}$ exponent                                      |

| df mantissa⊲0:53>:= df[0:1]<9:35>                                                                                                                   |                                                               |

| Instruction Interpretation Process                                                                                                                  |                                                               |

| Run $\rightarrow$ (instruction $\leftarrow$ M[IC]; IC $\leftarrow$ IC+1; next                                                                       | fetch                                                         |

| instruction_execution)                                                                                                                              | execute                                                       |

| Instruction Set and Instruction Execution Process                                                                                                   |                                                               |

| Instruction_execution := (                                                                                                                          |                                                               |

| Operations on M: $M[e] \leftarrow f$ ; or $M[e] \leftarrow f(M[e])$ ;                                                                               |                                                               |

| STZ (:= op = 600) $\rightarrow M[e] \leftarrow 0;$                                                                                                  | * store zero                                                  |

| $MSP (:= (op = -1623) \land (c = 7)) \rightarrow M[e] \ll 0);$                                                                                      | make sign positive; 704 series only                           |

| $MSM \ (:= \ (op \ = \ -1623) \ \land \ (c \ = \ 6)) \ \rightarrow M[e] <\!\!\!\!\!\!\!S\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | make sign minus; 704 series only                              |

| Block transfer of data, $M \leftarrow M$ (704 series only)                                                                                          |                                                               |

| TMT (:= op = -1704) → (M[AC<21:35>: (AC<21:35> + e'<28:35>) } ←                                                                                     | -                                                             |

| M[AC<3:17>:(AC<3:17> + e'<28:35>)]);                                                                                                                |                                                               |

|                                                                                                                                                     |                                                               |

Single word data transmission to M, M [e] + Register STO (:= op = -600)  $\rightarrow$  (M[e]  $\leftarrow$  MQ); \* stors MQ SLO (:= op = -620)  $\rightarrow$  (M[e]<S,1:17>  $\leftarrow$  MQ<S,1:17>); \* store left half MQ STO (:= op = 601)  $\rightarrow$  (M[e]  $\leftarrow$  ACs); \* store SLW (:= op = 602)  $\rightarrow$  (M[e]  $\leftarrow$  AC1); \* store logical word STP (:= op = 630)  $\rightarrow$  (M[e]<S,1,2>  $\leftarrow$  AC<P,1,2>); \* store prefix STD (:= op = 622)  $\rightarrow$  (M[e]<3:17>  $\leftarrow$  AC<3:17>); \* stors decrement STT (:= op = 625)  $\rightarrow$  (M[e]<18:20>  $\leftarrow$  AC<18:20>); \* store tag STA (:= op = 621)  $\rightarrow$  (M[e]<21:35>  $\leftarrow$  AC<21:35>); \* store address STL (:= op = -625)  $\rightarrow$  (M[e]<21:35>  $\leftarrow$  1C); store instruction location counter STR (:=  $hi_{op} = -1$ )  $\rightarrow (M[0] < 21:35 > \leftarrow IC; IC \leftarrow 2$ ); store instruction location counter and trap STI (:= op = 604)  $\rightarrow$  (M[e]  $\leftarrow$  SI); stors indicators Double length data transmission to M from A DST (:= op = -603)  $\rightarrow$  (M[e]  $\square$ M[e+1]  $\leftarrow$  ACs  $\square$ MQ); double store Binary operation with AC: M[e] ← AC b M[e]; ORS (:= op = -602)  $\rightarrow$  (M[e]  $\leftarrow$  AC)  $\lor$  M[e]); \* or to storage ANS (:= op = 320)  $\rightarrow$  (M[e]  $\leftarrow$  AC7  $\land$  M[e]); \* and to storage 6 bit character to M from AC, (7040 only); SAC (:= op = -1623)  $\rightarrow$  (M[e]<c x 6 : (c x 6+5)>  $\leftarrow$  AC<30:35>); Operations to the AC,MQ, or ACDMQ with AC,MQ,ACMQ, Keys and M operands:  $\mathsf{CLM} \ (:= \ (\mathsf{op} = 760) \ \land \ (e^{1} = 0)) \ \rightarrow (\mathsf{AC} \triangleleft \mathsf{Q}, \mathsf{P}, \mathsf{I}: \mathsf{35} \mathsf{>} \leftarrow 0);$ clear magnitude  $SSP (:= (op = 760) \land (e^{1} = 3)) \rightarrow (AC < S \leftarrow 0);$ \* set sign plus SSM (:= (op = -760)  $\land$  (e' = 3))  $\rightarrow$  (AC $\langle$ S>  $\leftarrow$  1); \* set sign minus CLA (:= op = 500)  $\rightarrow$  (AC  $\leftarrow$  0; next ACs  $\leftarrow$  AC+M[e]); clear and add CAL (:= op = -500)  $\rightarrow$  (AC  $\leftarrow$  0; next AC1  $\leftarrow$  AC1+M[e]); clear and add logical CLS (:= op = 502)  $\rightarrow$  (AC  $\leftarrow$  0; next AC  $\leftarrow$  AC-M[e]); clear and subtract LDQ (:= op = 560)  $\rightarrow$  (MQ  $\leftarrow$  M[e]); load MQ ENK (:= (op = 760)  $\land$  (e<sup>1</sup> = 4))  $\rightarrow$  (MQ  $\leftarrow$  Keys); enter Keys PIA (:= op = -46)  $\rightarrow$  (AC  $\leftarrow$  SI); place indicators in AC DLD (:= op = 443)  $\rightarrow$  (ACsDMQ  $\leftarrow$  M[e]DM[e+1]); double load Operations with  $AC, AC \leftarrow f(AC)$ CHS (:= (op = 760)  $\land$  (e' = 2))  $\rightarrow$  (AC $\langle S \rangle \leftarrow \neg AC \langle S \rangle$ ); change sign  $\mathsf{COM} \ (:= (\mathsf{op} = 760) \land (e' = 6)) \rightarrow (\mathsf{AC} \triangleleft \mathsf{Q}, \mathsf{P}, 1:35 \succ \frown \neg \mathsf{AC} \triangleleft \mathsf{Q}, \mathsf{P}, 1:35 \succ); \quad \text{$`complement magnitude"}$ RND (:= op = 760)  $\land$  (e' = 10))  $\rightarrow$  MQ<1>  $\rightarrow$  AC  $\leftarrow$  AC + 1; \* round ERN (:= op = 760)  $\land$  (e' = 11))  $\rightarrow$  (AC  $\leftarrow$  round(ACMQ){sf}); \* floating round ALS (:= op = 767)  $\rightarrow$  (AC<Q,P,1:35>  $\leftarrow$  AC<Q,P,1:35> x 2<sup>SC</sup>); \* AC left shift ARS (:= op = 771)  $\rightarrow$  (AC<Q,P,I:35>  $\leftarrow$  AC<Q,P,I:35> / 2<sup>sc</sup>); \* AC right shift LLS (:= op = 763)  $\rightarrow$  (ACMQ'  $\leftarrow$  ACMQ'  $\times 2^{SC}$ ); \* long left shift LRS (:= op = 765)  $\rightarrow$  (ACMQ<sup>1</sup>  $\leftarrow$  ACMQ<sup>1</sup>/ 2<sup>SC</sup>); \* long right shift ACMQ'<0:71> := AC<Q,P,1:35>

MQ<1:35> LGL (:= op = -763)  $\rightarrow$  (ACMQ''  $\leftarrow$  ACMQ''  $\times$  2<sup>SC</sup> {logical}); \* logical left shift LGR (:= op = -765)  $\rightarrow$  (ACMQ''  $\leftarrow$  ACMQ'' / 2<sup>SC</sup> {logical}); \* logical right shift ACMQ''<0:72> := AC<Q,P,1:35>

MQ<S,1:35> RQL (:= op = -773)  $\rightarrow$  (MQ  $\leftarrow$  MQ  $\times$  2<sup>SC</sup> {rotate}); \* rotate MQ left Exchange of Data between registers, AC, and MQ XCA (:= op = 131)  $\rightarrow$  (AC  $\leftarrow$  MQ; MQ  $\leftarrow$  AC); exchange AC and MQ

```

XCL (:= op = -130) \rightarrow (MQ \leftarrow AC1; AC1 \leftarrow MQ; AC\langleS,Q> \leftarrow O);

exchange logical AC and MQ

6 bit character to AC from M (704 only)

PCS (:= op = -1505) → (AC<3D:35> ← M [e ]<(c x 6): (c x 6 + 5)>); place character from storage

Binary operations with M, AC \leftarrow AC \ b \ M;

ADD (:= op = 400) \rightarrow (AC \leftarrow AC + M[e]);

* add

ADM (:= op = 401) \rightarrow (AC \leftarrow AC + abs(M[e]));

* add magnitude

SUB (:= op = 4D2) \rightarrow (AC \leftarrow AC - M[e]);

* subtract

SBM (:= op = -400) \rightarrow (AC \leftarrow AC - abs(M[e]));

* subtract magnitude

MPY (:= op = 200) \rightarrow (ACMQ \leftarrow MQ \times M[e]; AC\triangleleft, P> \leftarrow 0);

* multiply

MPR (:= op = -200) \rightarrow (ACMQ \leftarrow MQ \times M[e]; next

* multiply and round

MQ \lt I > \rightarrow AC \leftarrow AC + 1; AC \lt Q, P > \leftarrow 0);

DVH (:= op = 220) \rightarrow (AC,MQ \leftarrow ACMQ / M[e]; next

Divide_check \rightarrow Run \leftarrow 0);

* divide or halt

DVP (:= op = 221) \rightarrow (AC, MQ \leftarrow ACMQ / M[e]);

* divide or proceed; Divide_check may be set

ACL (:= op = 361) \rightarrow (AC1 \leftarrow AC1 + M[e]);

* add and carry logical word

The following are variable length x and / operations. C' specifies the length of divisor or multiplier.

VLM (:= op = 2D4) \rightarrow (ACMQ \leftarrow MQ \times M[e] {v1});

variable length multiply

VDP (:= op = 225) \rightarrow (AC,MQ \leftarrow ACMQ / M[e] {v1});

variable length divide or proceed

VDH (:= op = 224) \rightarrow (AC,MQ \leftarrow ACMQ / M[e] {v1}; next

variable length divide or halt

Divide_check \rightarrow Run \leftarrow 0);

Single precision floating point

FAD (:= op = 30D) \rightarrow (AC,MQ \leftarrow AC + M[e] {sf});

* add

FAM (:= op = 304) \rightarrow (AC,MQ \leftarrow AC + abs(M[e]) {sf});

* add magnitude

FSB (:= op = 302) \rightarrow (AC,MQ \leftarrow AC - M[e] {sf});

* subtract

FSM (:= op = 306) \rightarrow (AC, MQ \leftarrow AC - abs(M[e]) {sf});

* subtract magnitude

FMP (:= op = 260) \rightarrow (AC, MQ \leftarrow MQ \times M[e] {sf});

* multiply

FDH (:= op = 24D) \rightarrow (AC,MQ \leftarrow AC / M[e] {sf}: next

* divide or halt

Divide_check \rightarrow Run \leftarrow D);

FDP (:= op = 241) \rightarrow (AC, MQ \leftarrow AC / M[e] {sf});

* divids or proceed

Unnormalized single precision floating point

* add

UFA (:= op = -300) \rightarrow (AC,MQ \leftarrow AC + M[e] {suf});

UAM (:= op = -3D4) \rightarrow (AC,MQ \leftarrow AC + abs(M[e]) {suf});

* add magnitude

UFS (:= op = -3D2) \rightarrow (AC,MQ \leftarrow AC - M[e] {suf});

* subtract

USM (:= op = -3D6) \rightarrow (AC,MQ \leftarrow AC - abs(M[e]) {suf});

* subtract magnitude

UFM (:= op = -260) \rightarrow (AC,MQ \leftarrow MQ \times M[e] {suf});

* multiply

Double precision floating point

In DF operations, the SI are used as temporary registers and will be changed.

DFAD (:= op = 301) \rightarrow (

*add

ACMQ \leftarrow ACMQ + M[e]\squareM[e+1] {df}; SI \leftarrow?);

DFAM (:= op = 3D5) \rightarrow (

* add magnitude

ACMQ \leftarrow ACMQ + abs(M[e]\BoxM[e+1]) \{df\}; S1 \leftarrow ?);

DFSB (:= op = 303) \rightarrow (

* subtract

ACMO ← ACMO - M[e] □ M[e+1] {df }; SI ←?);

DFSM (:= op = 307) → (

* subtract magnitude

ACMO \leftarrow ACMQ - abs (M[e] \square [e+1]) {df }: SI \leftarrow?);

```

```

* multiplu

DFMP (:= op = 261) \rightarrow (

ACMO \leftarrow ACMQ \times M[e]\squareM[e+1] {df}; S1 \leftarrow ?);

* divide or halt

DFDM (:= op = -240) \rightarrow (

ACMQ ← ACMQ / M[e]□M[e+1] {df}; SI ← ?; next

Divide_check \rightarrow Run \leftarrow 0);

* divide or proceed; Divide check may be set

DFDP (:= op = -241) \rightarrow (

ACMQ \leftarrow ACMQ / M[e] \square M[e+1] {df}; SI \leftarrow ?);

Unnormalized double precision floating point

* add

DUFA (:= op = -301) \rightarrow (

ACMQ \leftarrow ACMQ + M[e]\squareM[e+1] {duf}; SI \leftarrow?);

* add magnitude

DUAM (:= op = -305) \rightarrow (

ACMQ \leftarrow ACMQ + abs(M[e]\squareM[e+1]){undf}; S1 \leftarrow?);

* subtract

DUFS (:= op = -303) \rightarrow (

ACMQ \leftarrow ACMQ - M[e]\bigcircM[e+1] {duf}; S1 \leftarrow?);

* subtract magnitude

DUSM (:= op = -307) \rightarrow (

ACMQ \leftarrow ACMQ - abs(M[e]\BoxM[e+1]){duf}; S1 \leftarrow?);

* multiply

DUFM (:= op = -261) \rightarrow (

ACMO \leftarrow ACMO \times M[e]\BoxM[e+1] {duf}; SI \leftarrow?);

Logical

ORA (:= OD = -501) \rightarrow (AC1 \leftarrow AC1 \lor M[e]);

* or to accumulator

ANA (:= op = -32D) \rightarrow (AC1 \leftarrow AC1 \land M[e]);

* and to accumulator

ERA (:= op = 322) \rightarrow (AC1 \leftarrow AC1 \oplus M[e]);

* exclusive or to accumulator

The convert instructions are not described in detail. These instructions take a table in memory, addressed by the 6, 6 bit characters in AC or MQ and form a sum of products in the AC or MQ for each character component of the word.

CVR (:= op = 114) \rightarrow (AC, MQ \leftarrow f(AC, C, XR[1], M[Y:Y+63]));

convert by replacement from the AC

CRQ (:= op = -154) \rightarrow (AC,MQ \leftarrow f(MQ,C,XR[1],M[Y:Y+63]));

convert by replacement from the MQ

CAQ (:= op = -114) \rightarrow (AC,MQ \leftarrow f(AC,MQ,C,XR[1],M[Y:Y+63]));

convert by addition from the MQ

Transmission between M, XR[T], and AC

If tag, T,=0, then a no operation occurs

PDX (:= op = -734) \rightarrow (XR[T] \leftarrow AC<3:17>);

* place decrement in index

PAX (:= op = 734) \rightarrow (XR[T] \leftarrow AC<21:35>);

* place address in index

PDC (:= op = -737) \rightarrow (XR[T] \leftarrow 2^{15} - AC < 3:17>);

* place complement of decrement in index

PAC (:= op = 737) \rightarrow (XR[T] \leftarrow 2^{15} - AC < 21:35 >);

* place complement of address in index

LX0 (:= op = -534) \rightarrow (XR[T] \leftarrow M[Y]<3:17>);

* load index from decrement

LXA (:= op = 534) \rightarrow (XR[T] \leftarrow M[Y]<21:35>);

* load index from address

LDC (:= op = -535) \rightarrow (XR[T] \leftarrow 2^{15} - M[Y] < 3:17>);

* load complement of decrement in index

LAC (:= op = 535) \rightarrow (XR[T] \leftarrow 2^{15} - M[Y] < 21:35>);

* load complement of address in index

AXT (:= op = 774) \rightarrow (XR[T] \leftarrow Y);

* address to index true

AXC (:= op = -774) \rightarrow (XR[T] \leftarrow 2^{15} - Y):

* address to index complement

PXO (:= op = -754) \rightarrow (AC \leftarrow 0; next AC\triangleleft:17>\leftarrowXR[T]);

* place index in decrement

PXA (:= op = 754) → (AC ← 0; next AC<21:35> ← XR[T]);

* place index in address

PCD (:= op = -756) → (AC ← 0; next AC <3:17> ← 2^{15} - XR[T]);

* place complement of index in decrement

PCA (:= op = 756) → (AC ← 0; next AC <21:35> ← 2^{15} - XR[T]);

* place complement of index in address

SXD (:= op = -634) \rightarrow (M[Y]\triangleleft:17> \leftarrow XR[T]);

* store index in decrement

SXA (:= op = 634) \rightarrow (M[Y]<21:35> \leftarrow XR[T]);

* store index in address

```

```

SCO (:= op = -636) \rightarrow (M[Y]\leq3:17> \leftarrow 2^{15} - XR[T]);

SCA (:= op = 636) \rightarrow (M[Y]<21:35> \leftarrow 2^{15} - XR[T]);

Transmission to Sense Indicators

PAI (:= op = 44) \rightarrow (SI \leftarrow AC1);

LDI (:= op = 441) \rightarrow (SI \leftarrow M[e]);

\mathsf{OAI} \ (:= \mathsf{op} = 43) \rightarrow (\mathsf{SI} \leftarrow \mathsf{SI} \lor \mathsf{AC1});

RIA (:= op = -42) \rightarrow (SI \leftarrow SI \land \neg ACI);

||A|(:= op = 41) \rightarrow (St \leftarrow SI \oplus AC1);

OSI (:= op = 442) \rightarrow (SI \leftarrow SI \lor M[e]);

RIS (:= op = 445) \rightarrow (SI \leftarrow SI \land \neg M[e]);

IIS (:= op = 440) \rightarrow (SI \leftarrow SI \oplus M[e]);

SIL (:= op = -55) \rightarrow (SI<0:17> \leftarrow SI<0:17> \lor R);

RIL (:= op = -57) \rightarrow (SI\triangleleft:17> \leftarrow SI\triangleleft:17> \land \neg R);

IIL (:= op = -51) \rightarrow (SI\triangleleft:17> \leftarrow SI\triangleleft:17> \oplus R);

SIR (:= op = 55) \rightarrow (SI<18:35> \leftarrow SI<18:35> \lor R);

RIR (:= op = 57) \rightarrow (SI<18:35> \leftarrow SI<18:35> \land \neg R);

\mathsf{IIR} (:= \mathsf{op} = 51) \rightarrow (\mathsf{S1} < 18:35 > \leftarrow \mathsf{S1} < 18:35 > \oplus \mathsf{R});

Program flow control instructions

NOP (:= op = 761) \rightarrow:

HPR (:= op = 420) \rightarrow (Run \leftarrow 0);

HTR (:= op = 0) \rightarrow (Run \leftarrow 0; iC \leftarrow e);

TRA (:= op = 20) \rightarrow (iC \leftarrow e);

XEC (:= op = 522) \rightarrow (instruction \leftarrow M[e]; next

Instruction_execution);

Conditional transfers

TZE (:= op = 100) \rightarrow ((AC<Q, P, 1:35> = 0) \rightarrow IC \leftarrow e);

TNZ (:= op = -100) \rightarrow (\neg (AC \triangleleft Q, P, I:35) = 0) \rightarrow IC \leftarrow e);

TPL (:= op = 120) \rightarrow (\neg AC < S > \rightarrow IC \leftarrow e);

TMI (:= op = -120) \rightarrow (AC<S> \rightarrow IC \leftarrow e);

TOV (:= op = 140) \rightarrow (AC_overflow \rightarrow 1C \leftarrow e;

AC_overflow \leftarrow 0;

TNO (:= op = -140) \rightarrow (\neg AC_overflow \rightarrow IC \leftarrow e;

AC, overflow \leftarrow 0;

TQP (:= op = 162) \rightarrow (\neg MQ<S> \rightarrow IC \leftarrow e);

TQO (:= op = 161) \rightarrow (MQ_overflow \rightarrow IC \leftarrow e;

HQ_overflow ← 0);

TLQ (:= op = 40) \rightarrow ((AC > MQ) \rightarrow IC \leftarrow e);

TIO (:= op = 42) \rightarrow ((AC1 = (AC1 \land SI)) \rightarrow 1C \leftarrow e);

TIF (:= op = 46) \rightarrow ((0 = (AC1 \land SI)) \rightarrow 1C \leftarrow e);

Index manipulation and control and subroutine calling

TSX (:= op = 74) \rightarrow (XR[T] \leftarrow 2^{15} - 1C; 1C \leftarrow Y);

TSL (:= op = -1627) \rightarrow (M[e]<2]:35> \leftarrow IC; IC \leftarrow e + 1);

Loop control

TXI (:= hi_{\cup}op = 1) \rightarrow (XR[T] \leftarrow XR[T] + 0; IC \leftarrow Y);

TXH (:= hi_{\cup}op = 3) \rightarrow ((0 < XR[T]) \rightarrow IC \leftarrow Y);

```

\* store complement of index in decrement \* store complement of index in address place accumulator in indicators load indicators or accumulator to indicators reset indicators from accumulator invert indicators from accumulator or storags to indicators resst indicators from storage invert indicators from storage set indicators of left half reset indicators of left half invert indicators of left half sst indicators of right half resst indicators of right half invert indicators of right half no operation \* halt and proceed \* halt and transfer \* transfer execute \* transfer on zero \* transfer on no zero \* transfer on plus \* transfer on minus \* transfer on overflow \* transfer on no overflow \* transfer on MQ plus \* transfer on MQ overflow \* transfer on low MQ \* transfer when indicators on \* transfer when indicators off

- \* transfer and set index

- \* 704

- \* transfer with index incremented

- \* transfer on index high

```

TXL (:= hi_op = -3) \rightarrow ((D \geq XR[T]) \rightarrow IC \leftarrow Y);

* transfer on index low or equal

TIX (:= hi op = 2) \rightarrow ((XR[T] > D) \rightarrow (XR[T] \leftarrow XR[T] - D;

* transfer on index

IC \leftarrow Y));

TNX (:= hi_op = -2) \rightarrow ((XR[T] > D) \rightarrow XR[T] \leftarrow XR[T] - D;

* transfer on no index

(XR[T] \leq D) \rightarrow IC \leftarrow Y);

Skip tests

MIT (:= (op = -1341) \land (c = 7)) \rightarrow (M[e] < S \rightarrow IC \leftarrow IC + 1);

storage minus test; 704 series only

PLT (:= (op = -1341) \land (c = 6)) \rightarrow (\neg M[e]<S> \rightarrow IC \leftarrow IC + 1); storage plus test; 704 series only

CCS (:= ((op = -1341) ∧ (c < 6)) → (

compare

(AC < 30:35) = M[e] < (c \times 6): (c \times 6 + 5) \rightarrow IC \leftarrow IC + 1;

character with storage; 704 series only

(AC < 30:35) < M[e] < (c \times 6): (c \times 6 + 5) >) \rightarrow IC \leftarrow IC + 2));

PBT (:= (op = -760) \land (e<sup>11</sup> = 1)) \rightarrow (AC<P> \rightarrow IC \leftarrow IC + 1);

* P bit test

DCT (:= (op = +760) \land (e'' = 12)) \rightarrow (Divide_check \rightarrow IC \leftarrow IC + 1)* Divide_check test

LBT (:= (op = +760) \land (e'' = 1)) \rightarrow (AC<35> \rightarrow IC \leftarrow IC + 1);

* low bit test

ZET (:= op = +520) \rightarrow ((M[e] = 0) \rightarrow IC \leftarrow IC + 1);

* storage zero test