# Chapter 37

# Intel Microprocessors: 8008 to 80861

Stephen P. Morse / Bruce W. Ravenel / Stanley Mazor / William B. Pohlman

# I. Introduction

"In the beginning Intel created the 4004 and the 8008."

# A. The Prophecy

Intel introduced the microprocessor in November 1971 with the advertisement, "Announcing a New Era in Integrated Electronics." The fulfillment of this prophecy has already occurred with the delivery of the 8008 in 1972, the 8080 in 1974, the 8085 in 1976, and the 8086 in 1978. During this time, throughput has improved 100-fold, the price of a CPU chip has declined from \$300 to \$3, and microcomputers have revolutionized design concepts in countless applications. They are now entering our homes and cars.

Each successive product implementation depended on semiconductor process innovation, improved architecture, better circuit design, and more sophisticated software, yet upward compatibility not envisioned by the first designers was maintained. This paper provides an insight into the evolutionary process that transformed the 8008 into the 8086, and gives descriptions of the various processors, with emphasis on the 8086.

# **B.** Historical Setting

In the late 1960s it became clear that the practical use of large-scale integrated circuits (LSI) depended on defining chips having

- High gate-to-pin ratio

- Regular cell structure

- Large standard-part markets

In 1968, Intel Corporation was founded to exploit the semiconductor memory market, which uniquely fulfilled these criteria. Early semiconductor RAMs, ROMs, and shift registers were welcomed wherever small memories were needed, especially in calculators and CRT terminals. In 1969, Intel engineers began to study ways of integrating and partitioning the control logic functions of these systems into LSI chips.

At this time other companies (notably Texas Instruments) were

exploring ways to reduce the design time to develop custom integrated circuits usable in a customer's application. Computeraided design of custom ICs was a hot issue then. Custom ICs are making a comeback today, this time in high-volume applications which typify the low end of the microprocessor market.

An alternate approach was to think of a customer's application as a computer system requiring a control program, I/O monitoring, and arithmetic routines, rather than as a collection of specialpurpose logic chips. Focusing on its strength in memory, Intel partitioned systems into RAM, ROM, and a single controller chip, the central processor unit (CPU).

Intel embarked on the design of two customer-sponsored microprocessors, the 4004 for a calculator and the 8008 for a CRT terminal. The 4004, in particular, replaced what would otherwise have been six customized chips, usable by only one customer. Because the first microcomputer applications were known, tangible, and easy to understand, instruction sets and architectures were defined in a matter of weeks. Since they were programmable computers, their uses could be extended indefinitely.

Both of these first microprocessors were complete CPUs-on-achip and had similar characteristics. But because the 4004 was designed for serial BCD arithmetic while the 8008 was made for 8-bit character handling, their instruction sets were quite different.

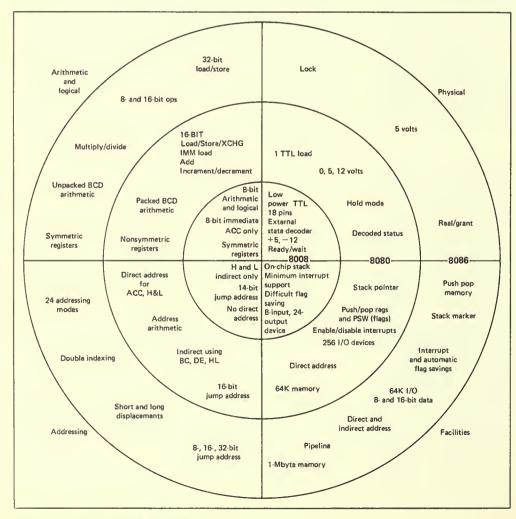

The succeeding years saw the evolutionary process that eventually led to the 8086. Table 1 summarizes the progression of features that took place during these years.

# II. 8008 Objectives and Constraints

Late in 1969 Intel Corporation was contracted by Computer Terminal Corporation (today called Datapoint) to do a pushdown stack chip for a processor to be used in a CRT terminal. Datapoint had intended to build a bit-serial processor in TTL logic using shift-register memory. Intel counterproposed to implement the entire processor on one chip, which was to become the 8008. This processor, along with the 4004, was to be fabricated using the then-current memory fabrication technology, *p*-MOS. Due to the long lead time required by Intel, Computer Terminal proceeded to market the serial processor and thus compatibility constraints were imposed on the 8008.

Most of the instruction-set and register organization was specified by Computer Terminal. Intel modified the instruction set so the processor would fit on one chip and added instructions to make it more general-purpose. For although Intel was developing the 8008 for one particular customer, it wanted to have the option of selling it to others. Intel was using only 16- and 18-pin packages in those days, and rather than require a new package for what was believed to be a low-volume chip, they chose to use 18 pins for the 8008.

|                           | 8008                   | 8080                                       | 8085                                       | 8086                                                           |

|---------------------------|------------------------|--------------------------------------------|--------------------------------------------|----------------------------------------------------------------|

| Number of<br>instructions | 66                     | 111                                        | 113                                        | 133                                                            |

| Number of<br>flags        | 4                      | 5                                          | 5                                          | 9                                                              |

| Maximum<br>memory size    | 16K bytes              | 64K bytes                                  | 64K bytes                                  | 1M bytes                                                       |

| I/O ports                 | 8 input<br>24 output   | 256 input<br>256 output                    | 256 input<br>256 output                    | 64K input<br>64K output                                        |

| Number of<br>pins         | 18                     | 40                                         | 40                                         | 40                                                             |

| Address bus<br>width      | 8†                     | 16                                         | 16                                         | 16†                                                            |

| Data bus<br>width         | 8†                     | 8                                          | 8                                          | 16†                                                            |

| Data types                | 8-bit unsign           | 8-bit unsign<br>16-bit unsign<br>(limited) | 8-bit unsign<br>16-bit unsign<br>(limited) | 8-bit unsign<br>8-bit signed<br>16-bit unsign<br>16-bit unsign |

|                           |                        | Packed BCD<br>(limited)                    | Packed BCD<br>(limited)                    | Packed BCD<br>Unpacked BCD                                     |

| Addressing<br>modes       | Register‡<br>Immediate | Memory direct<br>(limited)                 | Memory direct<br>(limited)                 | Memory direct<br>Memory indirect                               |

|                           |                        | Memory indirect<br>(limited)               | Memory indirect<br>(limited)               | Register<br>Immediate                                          |

|                           |                        | Register‡<br>Immediate                     | Register‡<br>Immediate                     | Indexing                                                       |

| Introduction<br>date      | 1972                   | 1974                                       | 1976                                       | 1978                                                           |

#### Table 1 Feature Comparison

† Address and date bus multiplexed.

‡ Memory can be addressed as a special case by using register M.

# III. 8008 Instruction-Set Processor

The 8008 processor architecture is quite simple compared to modern-day microprocessors. The data-handling facilities provide for byte data only. The memory space is limited to 16K bytes, and the stack is on the chip and limited to a depth of 8. The instruction set is small but symmetrical, with only a few operand-addressing modes available. An interrupt mechanism is provided, but there is no way to disable interrupts.

# A. Memory and I/O Structure

The 8008 addressable memory space consists of 16K bytes. That seemed like a lot back in 1970, when memories were expensive and LSI devices were slow. It was inconceivable in those days that anybody would want to put more than 16K of this precious resource on anything as slow as a microprocessor.

The memory size limitation was imposed by the lack of available

pins. Addresses are sent out in two consecutive clock cycles over an 8-bit address bus. Two control signals, which would have been on dedicated pins if these had been available, are sent out together with every address, thereby limiting addresses to 14 bits.

The 8008 provides eight 8-bit input ports and twenty-four 8-bit output ports. Each of these ports is directly addressable by the instruction set. It was felt that output ports were more important than input ports because input ports can always be multiplexed by external hardware under control of additional output ports.

One of the interesting things about that era was that, for the first time, the users were given access to the memory bus and could define their own memory structure; they were not confined to what the vendors offered, as they had been in the minicomputer era. As an example, the user had the option of putting I/O ports inside the memory address space instead of in a separate I/O space.

#### **B.** Register Structure

The 8008 processor contains two register files and four I-bit flags. The register files are referred to as the *scratchpad* and the *address stack*.

1. Scratchpad. The scratchpad file contains an 8-bit accumulator called A and six additional 8-bit registers called B,C,D,E,H, and L. All arithmetic operations use the accumulator as one of the operands and store the result back in the accumulator. All seven registers can be used interchangeably for on-chip temporary storage.

There is one pseudo-register, M, which can be used interchangeably with the scratchpad registers. M is, in effect, that particular byte in memory whose address is currently contained in H and L (L contains the eight low-order bits of the address and H contains the six high-order bits). Thus M is a byte in memory and not a register; although instructions address M as if it were a register, accesses to M actually involve memory references. The M register is the only mechanism by which data in memory can be accessed.

2. Address Stack. The address stack contains a 3-bit stack pointer and eight 14-bit address registers providing storage for eight addresses. These registers are not directly accessible by the programmer; rather they are manipulated with control-transfer instructions.

Any one of the eight address registers in the address stack can serve as the program counter; the current program counter is specified by the stack pointer. The other seven address registers permit storage for nesting of subroutines up to seven levels deep. The execution of a call instruction causes the next address register in turn to become the current program counter, and the return instruction causes the address register that last served as the program counter to again become the program counter. The stack will wrap around if subroutines are nested more than seven levels deep.

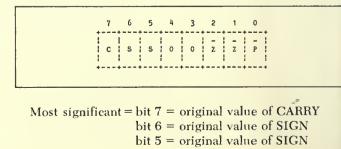

3. Flags. The four flags in the 8008 are CARRY, ZERO, SIGN, and PARITY. They are used to reflect the status of the latest arithmetic or logical operation. Any of the flags can be used to alter program flow through the use of the conditional jump, call, or return instructions. There is no direct mechanism for saving or restoring flags, which places a severe burden on interrupt processing (see Appendix I for details).

The CARRY flag indicates if a carry-out or borrow-in was generated, thereby providing the ability to perform multipleprecision binary arithmetic.

The ZERO flag indicates whether or not the result is zero. This provides the ability to compare the two values for equality.

The SIGN flag reflects the setting of the leftmost bit of the

result. The presence of this flag creates the illusion that the 8008 is able to handle signed numbers. However, there is no facility for detecting signed overflow on additions and subtractions. Furthermore, comparing signed numbers by subtracting them and then testing the SIGN flag will not give the correct result if the subtraction resulted in signed overflow. This oversight was not corrected until the 8086.

The PARITY flag indicates if the result is even or odd parity. This permits testing for transmission errors, an obviously useful function for a CRT terminal.

# C. Instruction Set

The 8008 instructions are designed for moving or modifying 8-bit operands. Operands are either contained in the instruction itself (immediate operand), contained in a scratchpad register (register operand), or contained in the M register (memory operand). Since the M register can be used interchangeably with the scratchpad registers, there are only two distinct operand-addressing modes immediate and register. Typical instruction formats for these modes are shown in Fig. 1. A summary of the 8008 instructions appears in Fig. 2.

The instruction set consists of scratchpad-register instructions, accumulator-specific instructions, transfer-of-control instructions, input/output instructions, and processor-control instructions.

The scratchpad-register instructions modify the contents of the M register or any scratchpad register. This can consist of moving data between any two registers, moving immediate data into a register, or incrementing or decrementing the contents of a register. The incrementing and decrementing instructions were not in Computer Terminal's specified instruction set; they were added by Intel to provide for loop control, thereby making the processor more general-purpose.

Most of the accumulator specific instructions perform operations between the accumulator and a specified operand. The operand can be any one of the scratchpad registers, including M, or it can be immediate data. The operations are add, add-withcarry, subtract, subtract-with-borrow, logical AND, logical OR, logical exclusive-OR, and compare. Furthermore, there are four unit-rotate instructions that operate on the accumulator. These instructions perform either an 8- or 9-bit rotate (the CARRY flag acts as a ninth bit) in either the left or right direction.

Transfer-of-control instructions consist of jumps, calls, and returns. Any of the transfers can be unconditional, or can be conditional based on the setting of any one of the four flags. Making calls and returns conditional was done to preserve the symmetry with jumps and for no other reason. A short one-byte form of call is also provided, which will be discussed later under interrupts.

Each of the jump and call instructions (with the exception of the one-byte call) specifies an absolute code address in the second and

| no operands                             |                                          |                                        |                            |

|-----------------------------------------|------------------------------------------|----------------------------------------|----------------------------|

|                                         |                                          |                                        |                            |

| *************                           |                                          |                                        |                            |

| opeode                                  |                                          |                                        |                            |

| *-*-*                                   |                                          |                                        |                            |

| one operand                             |                                          |                                        |                            |

| one operand                             |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

| : opcode : reg :                        | operand in regist                        | er                                     |                            |

| +-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-  |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

| +-+-+-+-+-+-+-+-+<br>lope: reg lopeod!  | operand in regist                        | er                                     |                            |

| +=+=+=+=+=+=+=+=+                       | ,                                        |                                        |                            |

| * = * = * = * = * = * = * = *           |                                          |                                        |                            |

| (ope) rp1 opcode)                       | operand in regist                        | er pair (60d0 only)                    |                            |

| +-+-+++++++++++++++++++++++++++++++++++ |                                          |                                        |                            |

| *=*=*=*=*=*=*                           |                                          |                                        |                            |

| opel rp! opcode!                        | indirect addressi                        | ng (8080 only)                         |                            |

| *-*-*                                   |                                          |                                        |                            |

| *-*-*                                   | ·····                                    |                                        |                            |

| opcode                                  | i data i                                 | iemediate operand                      |                            |

| *****                                   | +-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+- |                                        |                            |

| *-*-*-*                                 | *-*-*                                    | *****                                  | direct                     |

|                                         | addr-lo                                  | addr-hi                                | eddressing<br>(8080        |

| *-*-*-*-*-*                             | *-*-*-*-*-*-*                            | *-*-*-*                                | only)                      |

|                                         |                                          |                                        |                            |

| two operands                            |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

| *-************************************  | both openeda de                          | register                               |                            |

| lopel reg   reg                         | both operands in                         | reBigret.                              |                            |

|                                         |                                          |                                        |                            |

| lopel reg   ope ;                       | +-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+++      | one operand in reg<br>other is immedi- | ister,<br>ate operand      |

| +-+-+-+-+-+-+-+-+                       | +-+-+-+-+-+-+-+-+                        |                                        |                            |

|                                         | *-*-*-*-*-*-*-*-*                        | : addr-hi :                            | one operand<br>in register |

| lope; rpl opcode:                       | eddr-lo                                  | addr-hi                                | pair, other                |

| +-+-+-+-+-+-+-+                         | +-+-+-+-+-+                              | *-*-**                                 | is immediate               |

|                                         |                                          |                                        | operand<br>(8080 oniy)     |

| input/output                            |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

| *-*-*                                   |                                          |                                        |                            |

| lope: port ioi                          | (8005 only)                              |                                        |                            |

| *************                           |                                          |                                        |                            |

| *-**                                    | port                                     |                                        |                            |

|                                         |                                          | (8080 only)                            |                            |

| *-*-*                                   | +-+-+-+-+-+-+-+-+                        |                                        |                            |

|                                         |                                          |                                        |                            |

| jumps and calls                         |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

| **************************************  | · · · · · · · · · · · · · · · · · · ·    | //// addr-bi                           | (8008 0014)                |

| opcode                                  | addr-lo 1                                | ;///; ador-n1 ;<br>+-+-+-+-+-+-+-+-+   | (0000 00119)               |

|                                         |                                          |                                        |                            |

| i opcode i                              | addr-lo                                  | eddr-hi                                | (8080 only)                |

| +_+=+=+=+=+=+=+=+                       | +-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+- | +-+-+-+-+-+-+-+-+-+                    |                            |

|                                         |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

| 8008                                    | 0808                                     |                                        |                            |

| 000:A                                   | 000:B                                    | 8080                                   |                            |

| 001:8                                   | 007:0                                    |                                        |                            |

| 010:0                                   | 010:D                                    | 00:80                                  |                            |

| reg = 011:0<br>100:E                    | reg = 011:E pair<br>100:H                | = 01:0E<br>10:HL                       |                            |

| 101:6                                   | 101:L                                    | 11:SP                                  |                            |

| 110:L<br>111:M                          | 110:M<br>111:A                           |                                        |                            |

|                                         |                                          |                                        |                            |

|                                         |                                          |                                        |                            |

Fig. 1. Typical 8008 and 8080 instruction formats.

third byte of the instruction. The second byte contains the six high-order bits of the address, and the third byte contains the eight low-order bits. This inverted storage, which was to haunt all processors evolved from the 8008, was a result of compatibility with the Datapoint bit-serial processor, which processes addresses from low bit to high bit. This inverted storage did have a virtue in those early days when 256 by 8 memory chips were popular: it allowed all memory chips to select a byte and latch it for output while waiting for the six high-order bits which selected the chip. This speeded up memory access.

There are eight input instructions and 24 output instructions, which altogether use up 32 opcodes. Each of these instructions transfers a byte of data between the accumulator and a designated I/O port.

The processor-control instructions are halt and no-op. Halt puts the processor into a waiting state. The processor will remain in that state until an interrupt occurs. No-op is actually one of the move instructions; specifically, it moves the contents of the accumulator into the accumulator, thereby having no net effect (move instructions do not alter flag settings).

#### **D.** Interrupts

Interrupt processing was not a requirement of the 8008. Hence only the most primitive mechanism conceivable-not incrementing the program counter-was provided. Such a mechanism permits an interrupting device to jam an instruction into the processor's instruction stream. This is accomplished by having the interrupting device, instead of memory, respond to the instruction fetch; since the program counter isn't incremented, the instruction in memory that doesn't get fetched won't be skipped. The instruction typically supplied by the interrupting device is a call, so that an interrupt service routine can be entered and then the main program can be resumed after interrupt processing is complete (a jump instruction would result in the loss of the main program return address). To simplify the interrupting device's task of generating an instruction, the 8008 instruction set provides eight one-byte subroutine calls, each to a fixed location in memory.

There are no instructions provided for disabling the interrupt mechanism, and so this function must be realized with external hardware. More important, there are no instructions for conveniently saving the registers and flags when an interrupt occurs.

#### IV. Objectives and Constraints of the 8080

By 1973 the technology had advanced from p-MOS to n-MOS for memory fabrication. As an engineering exercise it was decided to use the 8008 layout masks with the n-MOS process to obtain a faster 8008. After a short study, it was determined that a new layout was required, so it was decided to enhance the processor at the same time, and to utilize the new 40-pin package made practical by high-volume calculator chips. The result was the 8080 processor.

The 8080 was the first processor designed specifically for the microprocessor market. It was constrained to include all the 8008

DO INSTRUCTION CODE OS D4 D3 O2 O1 90 01 MNEMONIC

DESCRIPTION OF OPERATION

ę affact Index Register Instructions The load instructions do not

| e carry.                                                                                                                                  |                                                                                             |                                                                                          |                                                                                        |                                                      |     |                                                       | -           |                                                                   |                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------|-----|-------------------------------------------------------|-------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| The load instructions do not affact the flag flip-flops. The increment and decrement instructions affect all flip-flops except the carry. | 11) MOV r1.r2 1 1 D D D S S S Load index register r1 with the content of index register r2. | (2) MOV r, M 1 1 D D D 1 1 1 Load index register r with the content of memory register M | MOV M.r 1 1 1 1 1 1 S S S Load memory register M with the content of index register r. | 0 0 D 0 D 1 1 0 Load index register r with date B B. |     | 0 0 1 1 1 1 1 0 Load memory register M with date B B. |             | D 0 D 0 0 0 0 1 Increment the content of index register r (r # A) | 0 0 D 0 D 0 0 1 Decremont the content of index register r (r # A). |

| The                                                                                                                                       | S                                                                                           | -                                                                                        | s                                                                                      | 0                                                    | 80  | 0                                                     | 8           | 0                                                                 | -                                                                  |

| ops.                                                                                                                                      | s                                                                                           | -                                                                                        | s                                                                                      | -                                                    | 8   | -                                                     | 8           | 0                                                                 | 0                                                                  |

| flip-fl                                                                                                                                   | s                                                                                           | -                                                                                        | s                                                                                      | -                                                    | 8   |                                                       | 8 8 8 8 8 8 | 0                                                                 | 0                                                                  |

| r flag                                                                                                                                    | ٥                                                                                           | ٥                                                                                        | -                                                                                      | ٥                                                    | 8   | -                                                     | 8           | ٥                                                                 | ٥                                                                  |

| ct the                                                                                                                                    | ٥                                                                                           | ٥                                                                                        | -                                                                                      | 0                                                    | 8   | -                                                     | 8           | 0                                                                 | 0                                                                  |

| ot affa                                                                                                                                   | ٥                                                                                           | ٥                                                                                        | -                                                                                      | ٥                                                    | 888 | -                                                     | 8           | ٥                                                                 | ٥                                                                  |

| do no                                                                                                                                     | -                                                                                           | -                                                                                        | -                                                                                      | 0                                                    | 8   | 0                                                     | 8           | 0 0                                                               | 0                                                                  |

| tions                                                                                                                                     |                                                                                             | -                                                                                        | -                                                                                      | o                                                    | 8   | 0                                                     | 8           | 0                                                                 | 0                                                                  |

| d instruc                                                                                                                                 | 0V r1.r2                                                                                    | OV r, M                                                                                  | OV M. r                                                                                | (3) MV1 r                                            |     | MV1 M                                                 |             | INR r                                                             | OCR r                                                              |

Accumulator Group Instructions

| The result of the ALU instructions after all of the flag flip-flops. The rotate instructions affect only the carry flip-flop. | Add the content of index register r, memory register M, or data | B B to the accumulator. An overflow (carry) sets the carry | flip-flop. |    | Add the content of index register r, memory register M, or data | B B from the accumulator with carry. An overflow (carry) sets | the carry flip-flop. |   | Subtract the content of index register r, memory register M, or | data B B from the accumulator, An underflow (borrow) sets | the carry flip-flop. |   | Subtract the content of index register r, memory M, or data | B B from the accumulator with borrow. An underflow (borrow) | sets the cerry flip-flop. |   | Compute the togical AND of the content of index register r, memory | register M, or deta B B with the accumulator. |     |   | Compute the EXCLUSIVE OR of the content of index register r. | memory register M, or data B B with the accumulator. |     |    | Compute the INCLUSIVE DR of the content of index register r, | memory register M, or data B B with the accumulator, |     |   | Compare the content of index register r, memory register M, or data | B B with the accumulator. The content of the accumulator is | unchanged. |   | Rotate the content of the accumulator left. | Rotate the content of the accumulator right. | Rotete the content of the accumulator left through the carry. | Rotate the content of the accumulator right through the carry. |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------|------------|----|-----------------------------------------------------------------|---------------------------------------------------------------|----------------------|---|-----------------------------------------------------------------|-----------------------------------------------------------|----------------------|---|-------------------------------------------------------------|-------------------------------------------------------------|---------------------------|---|--------------------------------------------------------------------|-----------------------------------------------|-----|---|--------------------------------------------------------------|------------------------------------------------------|-----|----|--------------------------------------------------------------|------------------------------------------------------|-----|---|---------------------------------------------------------------------|-------------------------------------------------------------|------------|---|---------------------------------------------|----------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|

| g flip-                                                                                                                       | s                                                               | -                                                          | 0          | 8  | S                                                               | -                                                             | 0                    | 8 | S                                                               | 1                                                         | ¢                    | 8 | S                                                           | 1                                                           | ¢                         | 8 | s                                                                  | 1                                             | ¢   | 8 | s                                                            | -                                                    | Q   | 8  | s                                                            | -                                                    | 0   | 8 | s                                                                   | 1                                                           | 0          | 8 | 0                                           | •                                            | 0                                                             | •                                                              |

| he fla                                                                                                                        | s                                                               | -                                                          | 0          | 80 | s                                                               | -                                                             | •                    | 8 | S                                                               | -                                                         | •                    | 8 | s                                                           | -                                                           | 0                         | 8 | S                                                                  | -                                             | 0   | 8 | S                                                            | -                                                    | •   | 8  | s                                                            | -                                                    | 0   | 8 | s                                                                   | -                                                           | 0          | • | -                                           | -                                            | -                                                             | -                                                              |

| l of t                                                                                                                        | s                                                               | -                                                          | ~          | 8  | s                                                               | -                                                             | -                    | 8 | s                                                               | -                                                         | -                    | 8 | S                                                           | -                                                           | -                         | 8 | s                                                                  | -                                             | -   | 8 | s                                                            | -                                                    |     | -  | S                                                            | -                                                    | -   | 8 | s                                                                   | -                                                           | -          | 8 | ٩                                           | ٩                                            | ٥                                                             | •                                                              |

| ect el                                                                                                                        | 0                                                               | 0                                                          | 0          | 8  | -                                                               | -                                                             | -                    |   | 0                                                               | o                                                         | 0                    | m | -                                                           | -                                                           | -                         |   | 0                                                                  | 0                                             | 0   |   | -                                                            | -                                                    | -   |    | -                                                            | 0                                                    | ¢   | 8 |                                                                     | -                                                           | -          |   | •                                           | -                                            | 0                                                             | -                                                              |

| ns eft                                                                                                                        | 0                                                               | 0                                                          | 0          | 8  | 0                                                               | o                                                             | 0                    | - | -                                                               | -                                                         | -                    | 8 | -                                                           |                                                             | -                         |   | 0                                                                  | 0                                             | 0   | 8 | •                                                            | ¢                                                    | 0   | -  | -                                                            | -                                                    | -   | 8 | -                                                                   | -                                                           | ***        |   | •                                           | •                                            | -                                                             | -                                                              |

| uctio                                                                                                                         | 0                                                               | ٥                                                          | 0          | 8  | 0                                                               | 0                                                             | 0                    | 8 | 0                                                               | 0                                                         | 0                    | 8 | 0                                                           | 0                                                           | 0                         |   | -                                                                  | -                                             | -   | 8 | -                                                            | -                                                    | -   | 80 | -                                                            | -                                                    | -   | ۵ | -                                                                   | -                                                           | -          | • | •                                           | 0                                            | 0                                                             | 0                                                              |

| instr                                                                                                                         | 0                                                               |                                                            | 0          | 8  | 0                                                               | 0                                                             | 0                    |   | 0                                                               | 0                                                         | 0                    |   | Ģ                                                           | 0                                                           | 0                         |   |                                                                    | 0                                             | 0   | 8 | 0                                                            |                                                      | 0   | 8  | 0                                                            | _                                                    | ۵   |   |                                                                     | 0                                                           | ٥          | 8 |                                             |                                              | 。                                                             | 0                                                              |

| ALU                                                                                                                           | -                                                               | -                                                          | 0          | 8  | -                                                               |                                                               | 0                    |   |                                                                 | -                                                         | 0                    |   | -                                                           | -                                                           |                           |   | _                                                                  | -                                             | 0   |   | -                                                            | _                                                    |     |    |                                                              | _                                                    |     | 8 | _                                                                   | -                                                           | o          |   | 0                                           |                                              | •                                                             | o                                                              |

| The result of the                                                                                                             | ADDr                                                            | ADO M                                                      | AD1        |    | AOC r                                                           | ADC M                                                         | AC1                  |   | SUBr                                                            | SUBM                                                      | Ins                  |   | SBBr                                                        | SBB M                                                       | SB1                       |   | ANAr                                                               | ANA M                                         | AN1 |   | XRAr                                                         | XRAM                                                 | XR1 |    | ORAr                                                         | ORA M                                                | 0R1 |   | CMP r                                                               | CMP M                                                       | CP1        |   | RLC                                         | RRC                                          | RAL                                                           | RAR                                                            |

| Program Guarter and Stack Control Instruction         Program Guarter and Stack Control Instruction         Program Counter and Stack Control Instruction       D       Unconditionally jump to memory address $B_3 \dots B_3 B_2 \dots B_3$ (d) JMP       0       1       X       X       1       0       0       Location       D         Program Current       Program       C       C       O       O       Unconditionally jump to memory address $B_3 \dots B_3 P_2 \dots B_3$ D         Program       Z       X       B       B       B       B       B       D       Jump to memory address $B_3 \dots B_3 P_2$ D       D       Jump to memory address $B_3 \dots B_3 P_2$ D       D       Jump to memory address $B_3 \dots B_3 P_2$ D       D       Jump to memory address $B_3 \dots B_3 P_2$ D       D       Jum to memory address $B_3 \dots B_3 P_2$ D       D       Jum to memory address $B_3 \dots B_3 P_3$ D       D       Jum to memory address $B_3 \dots B_3 P_3$ D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D                                                      | MNEMONIC                  | D-1   | - 90   | OS     | 0° CL  | 03     | INSTRUCTION CODE<br>05 04 03 02 | 6  | 00 | DESCRIPTION OF OPERATION                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|--------|--------|--------|--------|---------------------------------|----|----|---------------------------------------------------------------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Counte                    | r and | d Stac | k Cont | trol 1 | Instru | ctions                          |    |    |                                                                           |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           | 0     | -      | ×      | ×      | ×      | -                               | 0  | 0  | Unconditionally jump to memory address B3 B3B2 B2.                        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           | 82    | 82     | 82     | 82     | 82     | 82                              | 82 |    |                                                                           |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                         | ×     | ×      | 83     | 83     |        |                                 |    |    |                                                                           |

| P2         P2         P2         P2         P2         P2         P2         P2         P2         P3         P3<                                                                                                                    | 'ZNL                      | 0     | -      | 0      | CA     | 1      | Ľ                               | 0  | 0  | Jump to memory address B3 B3B2 B2 if the condition flip.                  |

| X         X         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B                                                                                                                                                                         | ç                         | 82    | B2     | 82     | B2     |        |                                 |    |    |                                                                           |

| 0         1         1         C4         C3         0         0           12         24         25         1         C4         2         0         0           12         24         25         15         15         15         15         15         15           12         25         25         2         2         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         15         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         16         <                                                                                                                                                 |                           | ×     | ×      | 83     | 83     |        |                                 |    |    |                                                                           |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Z                         | 0     | -      |        | CA     | -      |                                 | 0  | 0  | Jump to memory address B3 B3B2 B2 if the condition flip-                  |

| X         H3         H3 </td <td>PE</td> <td>B2</td> <td></td> <td>82</td> <td>82</td> <td></td> <td></td> <td></td> <td></td> <td></td>     | PE                        | B2    |        | 82     | 82     |        |                                 |    |    |                                                                           |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           | ×     | ×      | 83     | 83     |        |                                 |    |    |                                                                           |

| RNZ         0         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         0         1         0         0         0         1         0         0         0         1         0         0         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                       | r.                        | 0     | -      | ×      | ×      | ×      | -                               | -  | 0  | Unconditionally call the subroutine at memory address B <sub>3</sub>      |

| X         89         89         89         89         89         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83         83 </td <td></td> <td>82</td> <td></td> <td>82</td> <td>82</td> <td></td> <td></td> <td></td> <td></td> <td></td>       |                           | 82    |        | 82     | 82     |        |                                 |    |    |                                                                           |

| POUL         0         1         0         C4         C3         0         1         0           PO         B2                                                                                                                                  |                           | ×     | ×      | 83     | . B3   |        |                                 |    |    |                                                                           |

| PO         B2         B3         B3<                                                                                                                    | CNZ.                      | 0     | -      | ¢      | C4     | -      |                                 | -  | 0  | Call the subroutine at memory address B3 B3B2B2 If the con-               |

| X         H3         H3 </td <td>CPO</td> <td>82</td> <td>82</td> <td>82</td> <td>82</td> <td></td> <td></td> <td></td> <td></td> <td>-</td> | CPO                       | 82    | 82     | 82     | 82     |        |                                 |    |    | -                                                                         |

| Z.         0         1         1         C.4         C3         0         1         0           PFE         B2         B2         B2         B2         B3         B4         B4         B4         B3         B4         B4         B4         B4         B4         B4                                                                                                                                  |                           | ×     | ×      | 83     | 83     |        |                                 |    |    |                                                                           |

| PE         B2         B2<                                                                                                                    | ïz,                       | 0     | -      | -      | U.     |        |                                 | -  | 0  | Call the subroutine at memory address B3 B3B2 B2 if the con-              |

| X         X         B3         B3 <td>CPE</td> <td>82</td> <td></td> <td>82</td> <td>82</td> <td></td> <td></td> <td></td> <td></td> <td>_</td>         | CPE                       | 82    |        | 82     | 82     |        |                                 |    |    | _                                                                         |

| 0         0         ×         ×         1         1           RNZ         0         0         ×         ×         1         1           IPO         0         0         C4         C3         0         1         1           IPO         i         i         C4         C3         0         1         1           IPO         1         i         C4         C3         0         1         1           IPO         1         C4         C3         0         1         1         1           IPO         3         A         A         1         0         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           | ×     | ×      | B3     | 83     |        |                                 |    |    |                                                                           |

| Z 0 0 0 C4 C3 0 1 1<br>0 0 1 C4 C3 0 1 1<br>0 0 A A A 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | o     | 0      | ×      | ×      | ×      | -                               | -  | -  | Unconditionally return (down one level in the stack),                     |

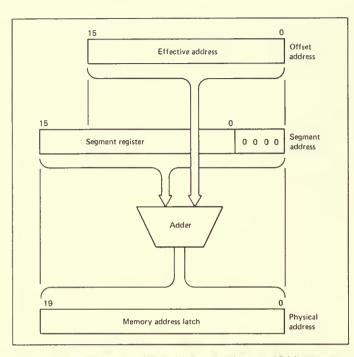

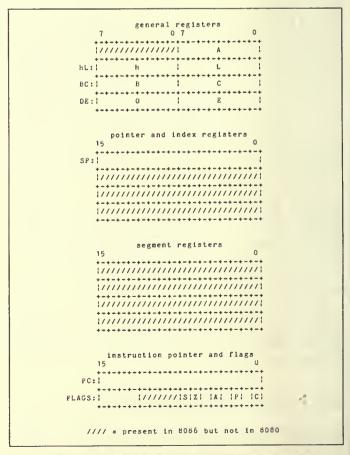

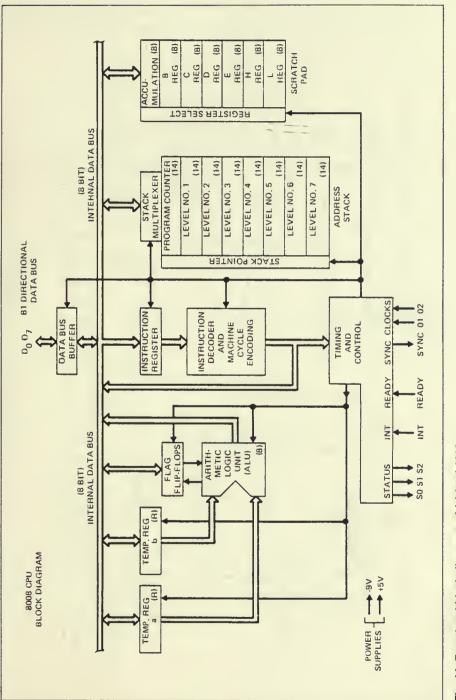

| 0 0 1 C4 C3 0 1 1<br>0 0 A A A 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C, RNZ,                   | 0     | 0      | 0      | C4     |        |                                 | -  | -  | Return (down one level in the stack) if the condition flip-flop is false, |