# Chapter 33 The IBM 1800

# Introduction

This third-generation computer is constructed with hybrid-circuit technology (semiconductors bonded to ceramic substrates) known as SLT (Solid Logic Technology). It has a core primary memory.

The 1800 is designed for process control and real-time applications. It is nearly identical to the IBM 1130, which is designed for small-scale, general-purpose, and scientific calculation applications. The two C's perform about the same for computation bound problems. The 1130 and 1800 are not program compatible with the "universal" IBM System/360 series, though introduced at about the same time. However, the 1800 uses terminals and secondary memories similar or identical to the System/360. These are organized about the standard IBM System/360 8-bit byte. Thus their common information media provide a link between the two. Hence an 1800 is sometimes connected to the System/360 as a preprocessor. The relative performance of the 1BM 1130, 1800, and the IBM System/360 can be seen on page 586. The 1800 has a better cost/performance ratio than a System/360, Model 40 and has the performance of a Model 30. From now on we will refer only to the IBM 1800, although much applies to the IBM 1130.

The 1800's interface facilities include a large number of T's which can connect to different physical processes; a multiple priority interrupt facility with fast response; multiple Pio's which can transfer information at high data rates;<sup>1</sup> and a complete instruction set for real-time, nonarithmetic processing.

We include the 1800 because it is a typical, 16-bit, real-time, process control computer. The ISP is the most straightforward of the IBM computers in the book (and perhaps the nicest). The several different Pio's and their implementations are unusual and should be carefully studied. Important aspects of the 1800 include the PMS structure as it links to real-time processes, e.g., analog processes; the straightforward Pc ISP (Appendix 1 of this chapter); the specialized Pio's for real-time T's; the Pc implementation; and the Pio implementation. The chapter is written to expose and explain these aspects.<sup>2</sup>

By comparing the 1800 with Whirlwind, an evolutionary progression can be seen. Their 1SP's are similar but, because of better technology, the 1800 shows an increase in capability. The 1800 Pc has a medium-sized state (ISP has six registers) including three index registers. The implementation is not elegant; a single register array and adder would provide the basis for a straightforward Pc implementation. The 1800 has features which facilitate higher information processing rates compared with Whirlwind. The major change between Whirlwind and the 1800 machines was brought about by the decreasing cost of registers and primary memory. In the 1800, all K's have independent memory (usually  $1 \sim 2$  words or characters) so that concurrent operation of almost all the T and Ms via their K's is possible. In contrast, Whirlwind has only a single, shared register in Pc, and only one device can operate at a time.

Lower hardware costs allow multiple Pio's in the 1800. The Pio's represent an unusual approach to information processing in this period. The Pio's which process standard disk, magnetic tape, and card reader are conventional, but the Pio's for analog and process signals are novel and interesting. The latter Pio's are the most unusual part of the 1800, and they allow independent programs in each Pio to do some very trivial processing tasks such as alarm-condition monitoring independent of Pc. However, the Pio's are limited; for example, it is difficult to transmit or receive a data block between Ms and Mp (using a Pio) without surrounding the data block with Pio control words (thereby transmitting the control words).

The interrupt system is typical of second- and third-generation computers and is comparable to the SDS 900 series (Chap. 42). In later computers interrupt conditions are used to determine a fixed address to which the processor interrupts. There are generally many conditions (100 to 1,000), but only a few discrete levels (8 to 20). The 1800 depends on program polling within a discrete interrupt level; each level has a unique, fixed address.

A principal ISP design problem is the addressing of the 65,536word Mp. Thus, a 16-bit number has to be generated within Pc for an address. In this regard the 1800 behaves like the 12-bit machines which have to address a  $2^{12}$  (4,096) word memory, and the modes or methods the 1800 uses for addressing are reasonable. It should be noted that it is relatively difficult to write programs which do not modify themselves. For example, the instruction, Store Status, is changed by its execution.

<sup>&</sup>lt;sup>1</sup>Although we refer to the data channels as Pio's, they have a very limited ISP for a Pio; in fact, they might better be called K's.

<sup>&</sup>lt;sup>2</sup>Some of the material in the chapter has been abstracted from the IBM 1800 Functional Characteristics Manual.

A peculiar feature of the 1800 is its storage protection (see page 408). This feature should provide program relocation capability in addition to protection, but it does not.

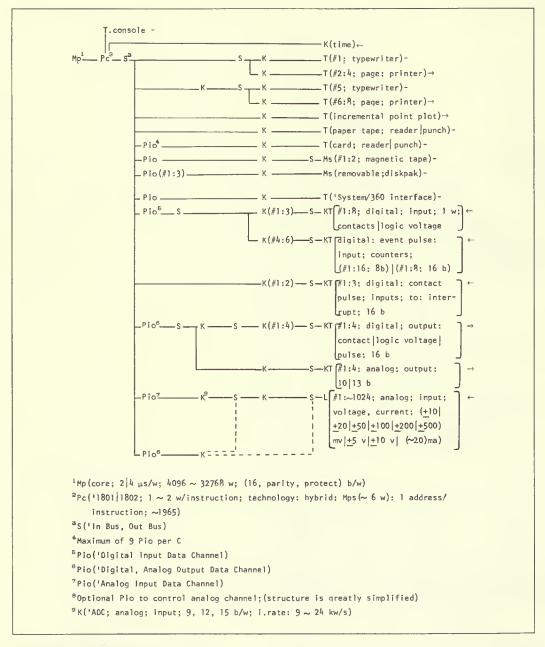

#### **PMS** structure

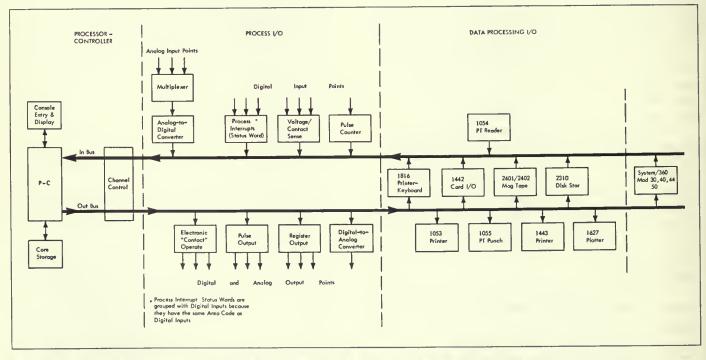

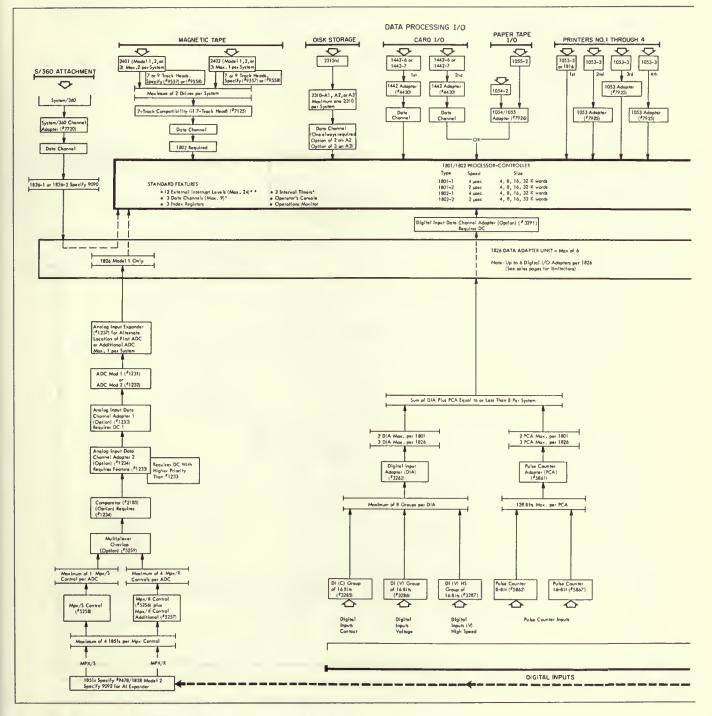

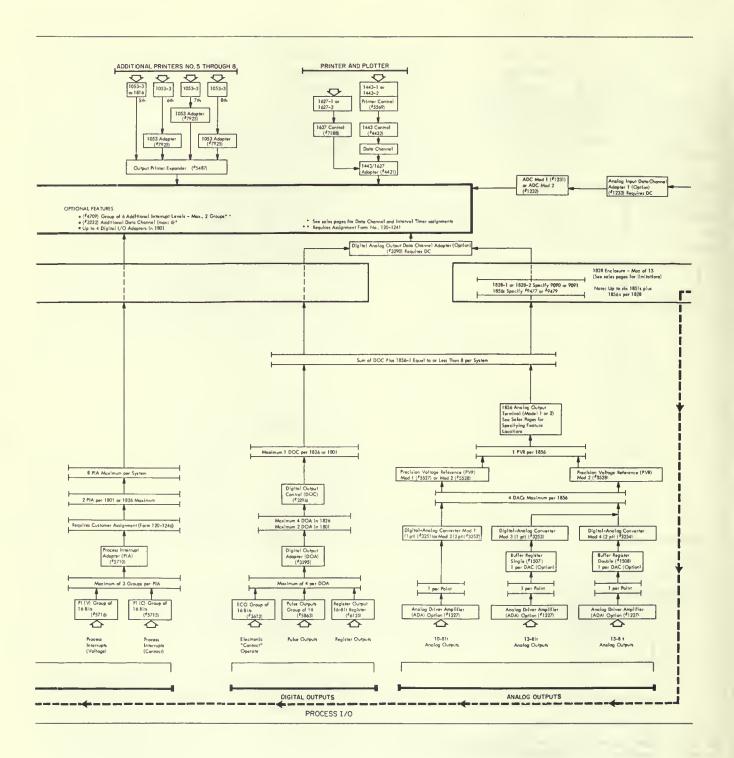

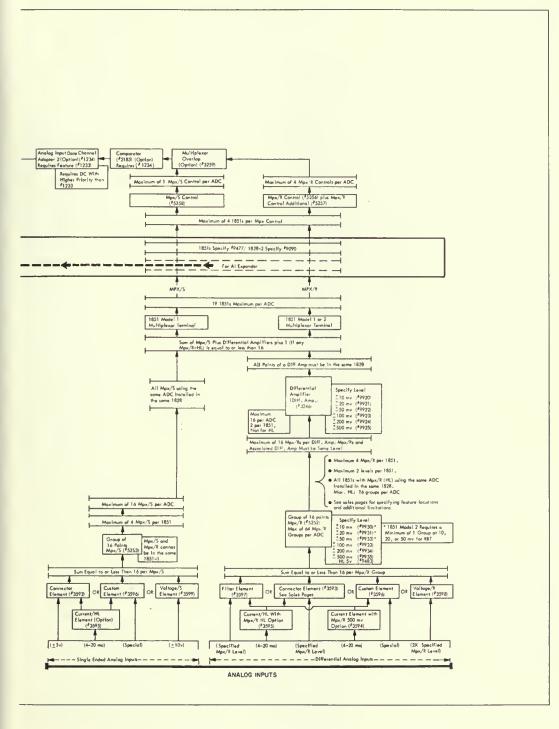

A simplified picture of the IBM 1800 structure is given in Fig. I, without Pio('Data Channel)'s and K('Device Adapter)'s. Each T and Ms have a K which connects Pc's In and Out Bus, the S('Pc to K). Some K's attach to Pio's and some directly to Pc. Information can be transferred between Mp and K via Pio at rates up to 0.5 megaword/s or 8 megabits/s. The IBM Configurator (Fig. 2) gives the restrictions on the possible structures, together with minute L details. It is presented as an alternative to the PMS structure (Fig. I). The Configurator is intended to show the "permissible structures" but does not show the logical or physical structure. The PMS diagram (Fig. 3) alternatively shows the physical-logical hardware structure and performance parameters. It should be noted that a PMS diagram with the information of the computer component Configurator (Fig. 2) would require slightly more details (and space).

#### The central processor<sup>1</sup>—primary memory

The IBM 1800 is a fixed-word-length, binary computer with 4, 8, 16, or 32-kword memories of 16 + 1 + 1 bits, and a memory cycle time of 2 or 4 microseconds. Of the 18 bits 1 bit is used as a parity check (P bit) and 1 bit is used for storage protection (S bit). The Pc instruction set operates on 16-bit and 32-bit words. Indirect addressing and three index registers are used in address modification. The Pc has a 24-level interrupt system, three interval timers, and a console.

The Pc interrupt is a forced branch (jump) in the normal program sequence based upon external or internal Pc conditions. The devices and conditions that cause interrupts are hardwired in fixed priority levels. An interrupt request is not honored while the level of the request itself or any higher level is being serviced, or if the level requested is masked. Examples of interrupt conditions are:

I An external process condition that requires attention is detected.

<sup>1</sup>IBM name: the Processor-Controller or PC.

Fig. 1. IBM 1800 data acquisition and control system. (Courtesy of International Business Machines Corporation.)

Fig. 2. IBM 1800 data-acquisition and control-system configurator. (Courtesy of International Business Machines Corporation.)

Chapter 33 The IBM 1800 403

.

404 Part 5 The PMS level

Fig. 3. IBM 1800 PMS diagram (simplified).

- 2 An interval timer has counted a previously set time interval.

- 3 A magnetic-tape drive has completed a data transfer previously requested and is ready for another request.

- 4 An operator has initiated an interrupt from the Pc console.

- 5 A device such as a typewriter has just printed a character and is ready to receive the next one.

# Primary-memory communication and data transmission with terminals and secondary memory

Two methods are used to transmit data between Mp and Ms, or Mp and T. First, low-speed devices are controlled directly by the program. Each character or word of data is transmitted to or from the Pc and onto T by means of an Execute I/O(XIO) instruction. The Pc program and device synchronization are accomplished by using the interrupt mechanism. Devices operating under direct program control include typewriter, printer, plotter, paper tape reader and punch, analog-to-digital converters, contact sense, voltage-level sense, pulse counters, etc.

The second method of transferring data is via the Pio('Data Channel)'s. The Pio program is started by the XIO instruction of the Pc. The transfer of data words then proceeds under control of the specified Pio, completely asynchronous to and in parallel with Pc program operation. The Pio gains Mp access independent of Pc (Pc operation is suspended for one Mp cycle). During the Mp cycle, the data are taken from or placed into core storage by Pio (via internal Pc control and registers). As soon as the Pio has been satisfied, which normally takes one cycle, the Pc proceeds. The logical state of the Pc, or the Instruction-set Processor, is not changed by Pio's access to Mp. This method of access is referred to as "cycle stealing." Devices (Ms and T) operating under Pio control include magnetic tapes, disks, line printer, card reader-punch, and the link to the IBM System/360.

Some devices can operate under both Pc and Pio control, depending on their characteristics and the configuration, e.g., analog input, analog output, digital input, and digital output.

#### Process I/O, controls and transducers

Analog inputs. Analog-input equipment includes analog-to-digital converters, multiplexors, amplifiers, and signal conditioning equipment to handle various analog-input signals. The data input rates are up to 20,000 I6-bit samples per second, with program selectable resolution and external synchronization. There can be 1,024 (via relay) and 256 (via high-speed solid state) multiplexed analoginput channels connected to a single K (analog-to-digital converter). The Configurator (Fig. 2) shows the allowable inputs. Digital inputs. The Digital Input provides up to 384 process interrupts; up to 1,024 bits of contact sense, digital input, or parallel register input; and 128 bits of event input counters as 1-, 8-, and 16-bit counting registers.

Analog outputs. Up to 128 analog outputs can be provided.

Digital outputs. Digital Outputs provide up to 2,048 bits of pulse output, contacts, and registers.

#### IO processors (data channels)

Pio('Data Channels) give a T or Ms the ability to communicate directly with Mp. For example, if an input unit requires a primary memory cycle to store data that it has collected, the Pio communicates directly with Mp and stores the data.

The Pio's run even if Pc is waiting. The Pio's have two registers: a Word Count which is used to count the number of words being transferred in a block between a device and Mp memory; and a Channel Address which points to the next word transferred in a block. The Channel Address is also used to select the next instruction in the program for the next block transfer task.

Two basic types of Pio's are used, nonchaining and chaining.<sup>1</sup> The Pio's provide the ability to transfer either a single block (nonchaining) or multiple blocks (chaining) directly to Mp independent of Pc.

#### The central processor

# Registers in the physical processor

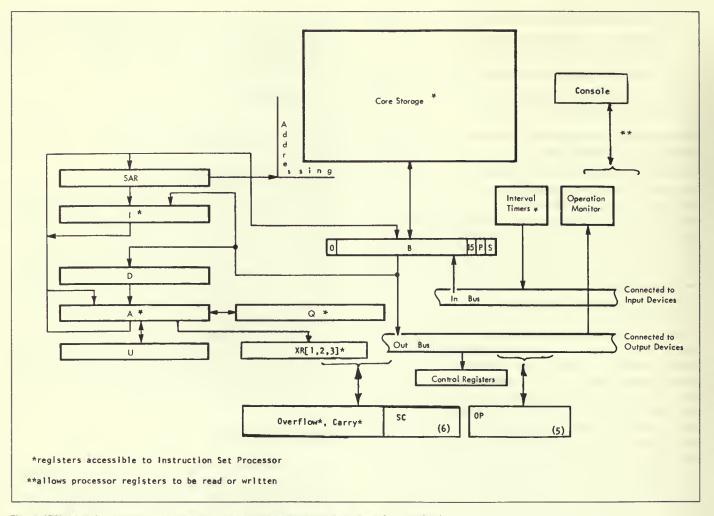

Figure 4 shows the relationship of the registers in Pc, together with those in the Instruction-set Processor. Those registers accessible by the program are shown with an °. All the registers are accessible from the console. A description of the functions of each register is given below.

Storage address register (SAR). All Pc references to Mp are selected or accessed by this 16-bit register. Pio references to Mp use the Channel Address Register (CAR) of the active Pio.

Instruction register  $(I)^{\circ}$ . This 16-bit counter register holds the address of the next instruction.

Storage buffer register (B). This 16-bit register is used for buffering all word transfers with Mp.

$^1\mathrm{A}$  descriptive name undoubtedly concocted by one of IBM's marketing departments.

Fig. 4. IBM 1800 Pc data flow. (Courtesy of International Business Machines Corporation.)

Arithmetic factor register (D). This I6-bit register is used to hold one operand for arithmetic and logical operations. The Accumulator provides the other factor.

Accumulator  $(A)^{\circ}$ . This 16-bit register contains the results of any arithmetic operation. It can be loaded from or stored into core storage, shifted right or left, and otherwise manipulated by specific arithmetic and logical instructions.

Accumulator extension  $(Q)^{\circ}$ . This register is a 16-bit low-order extension of the Accumulator. It is used during multiply, divide, shifting, and double-precision arithmetic.

Shift control counter (SC). This 6-bit counter is used primarily to control shift operations.

Accumulator temporary (U). The U register is used to store A temporarily during an instruction or an operation which requires the A's facilities.

OP register (OP). This 5-bit register is used to hold the operation code portion of an instruction.

Index registers<sup>\*</sup>. The three I6-bit registers are used in effectiveaddress calculations. Overflow and carry indicators<sup>°</sup>. The two indicator bits associated with the Accumulator are Overflow and Carry. The Overflow indicator can be turned on by Add, Subtract, or Divide instruction and indicates a result larger than can be represented in the Accumulator. The Overflow indicator can also be turned on by a Loadstatus instruction. Once Overflow is on, it will not be changed except by testing the indicator, or by a Load-status or Store-status instruction. The Carry indicator provides the information that a carry (or borrow) from the high-order position of the Accumulator has occurred.

The Carry indicator is used with the Add, Subtract, Shift-left, Load-status, Store-status, and Compare instructions.

In-bus. This 18-bit bus is a link(L) used to carry information from a K to Pc. Generally only 16 of the 18 bits are used, although transfers to magnetic tape can be made three 6-bit characters.

*Out-bus.* This 18-bit bus is used to carry information from Pc to a K.

#### Instruction-set processor

The operation of the Pc from a program viewpoint follows. The ISP registers were declared (°) in the previous section and in Fig. 4. The ISP registers are the I6-bit I, A, Q, XR [1, 2, 3], and the 1-bit Overflow and Carry.

An ISP description of the 1800 appears in Appendix I of this chapter. It is incomplete in the following respects: The memory protect bit checking is not described; the illegal (undefined) instruction action is not described; double word data must be aligned on even and odd address word boundaries or else a fault occurs; and the IO instruction and interrupt operation are not given.

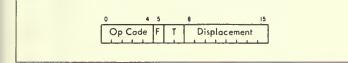

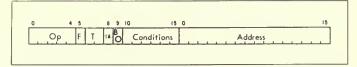

Instruction formats. Two basic instruction-word formats are used, one word (Fig. 5) and two word (Fig. 6). The bits within the instruction words are used in the following manner:

OP Operation Code. These 5 bits define the instruction.

Fig. 5. IBM 1800 one-word-instruction format. (Courtesy of International Business Machines Corporation.)

Fig. 6. IBM 1800 two-word-instruction format. (Courtesy of International Business Machines Corporation.)

- F Format bit. A 0 indicates a single-word instruction, and I a two-word instruction.

- T Tag. These 2 bits specify which of the three index registers is used in address modification or the shift count.

- DISP Displacement. These 8 bits are usually added to the instruction register or the index register specified by T for one-word instructions. The modified address is defined as the Effective Address (EA). If T is 00, the displacement is added to the instruction register (then EA = I + DISP). The displacement is in two's complement form if negative, with the sign in bit 8. The bit in position 8 is automatically extended to the higher-ordered bits (0 to 7) when the displacement is used in EA generation.

- IA Indirect addressing. This bit is used only in the two-word-instruction format. If 0, addressing will be direct. If a 1, addressing will be indirect. Only one level of indirect addressing is permitted. (The Load Index and Modify Index and Skip instructions have exceptions, as shown in the ISP description.)

- BO Branch Out. This bit is used to specify that the Branch or Skip on Condition (BSC) instruction is to be interpreted as a Branch Out (BOSC) when used in an interrupt routine.

- COND Conditions. These 6 bits select the indicators that are to be interrogated on a BSC or BSI instruction. The bit assignments for conditions are:

ADDRESS These 16 bits usually specify a core storage address

|                                      | $F = 0$ (direct addressing) $\dagger$                                                                                                                    | $(F = 1) \land (IA = 0)$<br>(direct addressing)                                                                                                         | $(F = 1) \land (IA = 1)$<br>(indirect addressing)                                                                                                                   |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T = 00<br>T = 01<br>T = 10<br>T = 11 | $\begin{array}{l} EA \leftarrow I + Disp \ddagger \\ EA \leftarrow XR[1] + Disp \\ EA \leftarrow XR[2] + Disp \\ EA \leftarrow XR[3] + Disp \end{array}$ | $\begin{array}{l} EA \leftarrow Address \\ EA \leftarrow Address + XR[1] \\ EA \leftarrow Address + XR[2] \\ EA \leftarrow Address + XR[3] \end{array}$ | $\begin{array}{l} EA \leftarrow C(Address) \\ EA \leftarrow C(Address + XR[1]) \\ EA \leftarrow C(Address + XR[2]) \\ EA \leftarrow C(Address + XR[3]) \end{array}$ |

#### Table 1 Determining effective addresses

+ Contents of instruction register (I) or index register (XR[1], XR[2], XR[3]).

‡ May be true positive quantity or negative two's complement quantity.

§ C specifies "contents" at location specified by Address or Address + XR[1], XR[2], or XR[3].

in a two-word instruction. The address can be modified by the contents of an index register or used as an indirect address if the IA bit is on.

*Effective-address generation.* The Effective Address (EA) is developed as shown in Table 1. The instruction set is divided into five classes as shown in Table 2.

Storage protection. The storage-protection facility protects the contents of specified individual locations of Mp from change due to the erroneous storing of information during the execution of a program. The status of each location is identified as "read only" or "read/write" by the condition of the Storage Protect Bit, S.

The Store-status instruction is used to write and clear Storage Protect Bits. The execution of this instruction is under control of the Write Storage Protect Bits switch on the console. Any attempt by the program to write into a read-only protected location results in a storage-protect violation which causes the Internal Interrupt (the highest priority interrupt).

#### Instruction interpretation process

The simplified Pc data-flow block diagram (Fig. 4) shows instructions and data entering and leaving memory via the B register. Additional bits in Pc hold the P and S bits for Mp. Input devices send data and instructions to the B register via the 18-bit In-bus. Output devices receive data from the B register via the 18-bit Out-bus. Eighteen bits can be transferred between Pc and K(magnetic tape). As each stored-program instruction is selected, its various parts (op code, format bit, etc.) are directed to the control registers via the B register and the Out-bus. The control registers decode and interpret each instruction before the instruction is executed.

Except for Pio operations, all instructions and data in memory are addressed by the Storage Address Register (SAR). SAR obtains the memory address from the I register or the A register. The

| Class      | Instruction                      | Indirect<br>addressing | Mnemonic |

|------------|----------------------------------|------------------------|----------|

| Load and   | Load accumulator                 | Yes                    | LD       |

| store      | Double load                      | Yes                    | LDD      |

|            | Store accumulator                | Yes                    | STO      |

|            | Double store                     | Yes                    | STD      |

|            | Load index                       | +                      | LDX      |

|            | Store index                      | Yes                    | STX      |

|            | Load status                      | No                     | LDS      |

|            | Store status                     | Yes                    | STS      |

| Arithmetic | Add                              | Yes                    | А        |

|            | Double add                       | Yes                    | AD       |

|            | Subtract                         | Yes                    | S        |

|            | Double subtract                  | Yes                    | SD       |

|            | Multiply                         | Yes                    | м        |

|            | Divide                           | Yes                    | D        |

|            | And                              | Yes                    | AND      |

|            | Or                               | Yes                    | OR       |

|            | Exclusive Or                     | Yes                    | EOR      |

| Shift      | Shift Left instructions:         |                        |          |

|            | Shift left logical (A)†          | No                     | SLA      |

|            | Shift left logical (AQ)†         | No                     | SLT      |

|            | Shift left and count (AQ)†       | No                     | SLC      |

|            | Shift left and count (A)†        | No                     | SLCA     |

|            | Shift Right instructions:        |                        |          |

|            | Shift right logical (A)†         | No                     | SRA      |

|            | Shift right arithmetically (AQ)† | No                     | SRT      |

|            | Rotate right (AQ)*               | No                     | RTE      |

| Branch     | Branch and store I               | Yes                    | BSI      |

|            | Branch or skip on condition      | Yes                    | BSC (BOS |

|            | Modify index and skip            | ‡                      | MDX      |

|            | Wait                             | No                     | WAIT     |

|            | Compare                          | Yes                    | CMP      |

|            | Double compare                   | Yes                    | DCM      |

| /0         | Execute I/O                      | Yes                    | XIO      |

|            |                                  |                        |          |

Table 2 Instruction set

† Letters in parentheses indicate registers involved in shift operations.

‡ See the section for the individual instruction (MDX and LDX).

contents of the I register are developed by one of the following means, depending on the Pc operation:

- I The I register is incremented for each instruction.

- 2 The effective address of each instruction is developed in the accumulator (A register) and then transferred to SAR. The contents of the accumulator are saved in an auxiliary (U) register during effective-address computation. If the instruction was a branch, the contents of SAR is transferred to the I register.

The following examples illustrate the data flow or instruction interpretation process for the Load Accumulator (LD) instruction.

# One-word load instruction Instruction Cycle

- 1 A register transfers to U register.

- 2 I register transfers to SAR (I register is then incremented).

- 3 SAR addresses the memory location containing the instruction.

- 4 Memory location transfers to the B register and Out-bus.

- 5 Control registers store various parts of the instruction (op code, format, and tag).

- 6 Displacement is stored in the D register.

- 7 a If tag = 00, I register transfers to A register. b If tag  $\neq$  00, the specified XR transfers to A register.

- 8 Displacement (D register) is added to A register.

#### Execute Cycle

- 9 A register transfers to SAR (effective address).

- 10 U register transfers to A register.

- II SAR addresses data word.

- 12 Data word transfers to B register.

- 13 B register loads into A register (via D register).

# Two-word load instruction, direct addressing Instruction Cycle 1

- I A register transfers to U register.

- 2 I register transfers to SAR (I register is then incremented).

- 3 SAR addresses the memory location containing the instruction (first word).

- 4 Memory location transfers to B register and Out-bus.

- 5 Control registers store various parts of the instruction (op code, format, and tag).

- 6 If  $tag \neq 00$ , the specified XR transfers to A register.

#### Instruction Cycle 2

- 7 I register transfers to SAR (I register is then incremented).

- 8 SAR addresses second word of instruction.

- 9 Second word of instruction (address) is read into B register.

- 10 Address (from B register) is stored in D register.

- II a If tag = 00, D register transfers to A register.

b If tag ≠ 00, D register is added to A register (A register contains contents of XR).

#### Execute Cycle

- 12 A register transfers to SAR (effective address).

- 13 U register transfers to A register.

- 14 SAR addresses memory at effective address (data word).

- 15 Data word transfers to B register.

- 16 B register loads into A register (through D register).

#### Central-processor communication with the controls<sup>1</sup>

#### Direct program control of the controls

Pc direct programmed control of I/O devices is on the basis of single-word or character-at-a-time transfers for each XIO instruction executed. One data word or character is transferred to or from Mp to K. The XIO instruction specifies an I/O Control Command (IOCC) with a function of Control, Sense, Read, or Write to a controlled device. This command is either directly to a device or to a Pio.

It is possible for the program sequence to execute an XIO instruction to a device that is busy responding to a previous XIO instruction. Each device has a Busy indicator, which signals whether or not the device can accept data or control information. (Incorrect program sequence timing may cause undetected errors.)

<sup>1</sup>IBM name: Adapter or Device Adapter.

110

It is possible for a device operating synchronously with the program to request a data word transfer before the program sequence is ready to service the request. Devices with this potential have a "program check" indicator to signal when data have been lost (that is, Pc has not kept up with the device).

#### Execute I/O instruction (XIO)

This instruction is used for programmed I/O operations and to initialize Pio; it may be either one or two words in length, as specified by the F bit. In the two-word instruction the address is either a direct or indirect address, as specified by the IA bit. For proper operation the effective address must be an even address. The effective address is used to select a two-word I/O Control Command (IOCC) from storage.

The IOCC specifies the I/O operation, I/O device, and core storage address. The format of the two-word IOCC follows, with an explanation of the assigned fields:

Area :=  $IOCC[1]\langle 0:4\rangle$ . The area field specifies a unique segment of I/O which may be a single device (1442 Card Read-Punch, 1443 Printer, etc.) or a group of several units (magnetic-tape drives, serial I/O units, contact sense units, etc.). (Area 00000 is used to address system devices such as the console and the Interrupt Mask Register.)

Function :=  $IOCC[1]\langle 5:7 \rangle$ . The primary I/O functions are specified by the 3-bit function code of the IOCC:

- 000 Removes an I/O device from on-line status and places it in a "free" mode.

- 001 Write Transfers a single word from storage to an I/O unit. The address of the storage location is provided by the Address field of the I/O Control Command.

- 010 Read Transfers a single word from an I/O unit to storage. The address of the storage location is provided by the Address field of the I/O Control Command.

- 011 Sense Interrupt Level Directs the selected I/O device to make its status available in the Accumulator as the Interrupt Level Status Word (ILSW).

- 100 Control Causes the selected device to interpret the address and/or Modifier of the IOCC as a specific control action. Examples are feed card and load interrupt mask register.

101 Initialize Write Initiates a Write operation on a device or unit which will subsequently make data transfers from storage via a Pc.

> Initialize Read Initiates a Read operation from a device or unit which will subsequently make data transfers to storage via a Data Channel.

111 Sense Device Reads the selected device status word into the Accumulator. A Device Status Word (DSW) and the Process Interrupt Status Word (PISW) are sensed with this instruction.

> If Area 00000 is specified, the Console status and Interval Timer status may be brought into the Accumulator as specified by a unit address code in the Modifier field.

The current contents of the Accumulator are destroyed by the execution of Sense Interrupt Level, Sense Device, Initialize Read, Initialize Write, Read, or Write.

Modifier :=  $IOCC[1]\langle 8:15 \rangle$ . This 8-bit field provides additional detail for either Function or Area. For example, if the Area specifies a disk and if the Function specifies Control (100) then a particular modifier code specifies the direction of the Seek operation. In this case, the Modifier serves to extend the function.

If, however, the Area specifies a group of I/O devices, and if the Function specifies Write (001), then the particular unit address is specified by the modifier.

Address :=  $IOCC[0]\langle 0:15 \rangle$ . The meaning prescribed for this 16-bit field is dependent upon the Function specified by this I/O Control Command:

- 1 If Function is Initialize Write (101) or Initialize Read (110), then Address specifies the starting address of a table in storage (an 1/O block). The contents of this table are data words and control information.

- 2 If Function is Control (100) and if, for example, Area specifies the 1443 Printer, the Address may specify a specific control action.

- 3 If Function is Sense (011 or 111), the Address field is ignored. Instead, an increment of time equivalent to a memory cycle is taken, during which the selected I/O device or Interrupt Level places its status word in the accumulator.

4 If Function is Write (001) or Read (010), the Address specifies the storage location of the data word.

#### XIO execution interpretation process

- I The EA of the XIO is developed in the accumulator (A) and routed to the Storage Address Register (SAR) to locate the IOCC (as for any EA).

- 2 Bit position I5 of SAR is forced on to select the EA + 1 where the IOCC Area, Function, and Modifier are found.

- 3 The Area, Function, and Modifier are routed through the B register to the Out-bus to the control of the device specified by the Area.

- 4 Bit position I5 of SAR is turned off to allow the address portion of the IOCC word to be transferred from the Mp location specified by the Effective Address (EA) to the B register.

- 5 If the Function is an Initialize Read, Initialize Write, or Control, the address part of the IOCC is routed through the B register to the Out-bus. The address part of the Initialize Read/Write IOCC goes to the Channel Address Register (CAR) of Pio. If the Function is Read or Write, the address is routed from the B register through the A register to the SAR. SAR addresses the memory location to or from which the data are transmitted.

#### Interval timers

Three timers are provided to supply real-time information to the program. They are in core-storage locations 0004 (Timer A), 0005 (Timer B), and 0006 (Timer C). Each timer is incremented according to its associated or permanent time base and can be hardwired to be 0.125, 0.250, 0.5, 1, 2, 4, 8, 16, 32, 64, or I28 milliseconds.

The timers can be started or stopped under program control. When the count reaches zero, an interrupt is requested on the level assigned to the timers.

#### Interrupt

The interrupt feature provides an automatic branch from the normal program sequence, based upon an external condition. A maximum of 24 external interrupt levels (groups) are available, arranged in order of priority. Twelve external interrupt levels are standard. Each interrupt level has a unique core-storage address assigned to it. Several devices may be connected to a single interrupt level, and program polling can be used to differentiate the possible signals causing the interrupt. The Interrupt Level Status Word, ILSW, is used to identify the specific condition causing its interrupt level to request service. Internal interrupt. When any one of the following error conditions occur, there is an internal interrupt in Pc: an invalid op code; a Mp parity error (an even number of bits); a storage-protect violation; and Channel Address Register check error. The internal interrupt takes priority over all external interrupts and cannot be masked.

A mask register exists for the masking and unmasking of interrupt levels. An interrupt level that is masked cannot initiate a request for service until it has been unmasked.

Device status word (DSW). DSW indicators usually fall into three general categories:

- I Error or exception interrupt conditions

- 2 Normal data or service-required interrupts

- 3 Routine status conditions

Process interrupt status word indicators (PISW). The PISW indicators are physically located in Pc and are turned on by events external to the computer, e.g., contact closures or voltage shifts.

### 10 processors<sup>1</sup>

The Pc initializes each Pio with an XIO instruction. The Pio has priority to the extent that, when the I/O device is ready to send or receive a data word, the Pc is stopped while the word transfers to or from core storage. Pc data and conditions are undisturbed except for the memory locations that receive data from an input device.

I/O devices that are to be operated concurrently must be on separate Pio's.

The XIO instruction for a Pio specifies an I/O Control Command (IOCC) with a function of Initialize Read or Initialize Write. However, even though a device operates with a Pio, the XIO instructions in Pc are used to sense device status and for control.

#### Registers

Channel address register. The Channel Address Register (CAR) is a I6-bit register used to store the Mp address of the next word that will be addressed by the Pio. Each Pio has a CAR. Pio and its associated CAR are selected when their assigned I/O device is selected by the Area Code and Modifier of an IOCC word. CAR is incremented by I after each transfer of its contents to CAB.

<sup>1</sup>IBM name: Data Channel (DC).

*Channel address buffer*. A common Channel Address Buffer (CAB) is used by all Channel Address Registers to address Mp. When a cycle steal request occurs, the CAR for the requesting Pio is transferred into the Channel Address Buffer.

Channel-address-register check bit. Channel Address Register (CAR) checking is provided to ensure that the first word addressed by a selected CAR is the first word of the correct data table. Thus the check determines if a Pc program has set up the Pio program correctly.<sup>1</sup> A CAR check is made for all devices after the address from the IOCC word is transferred to the selected CAR. A bit-by-bit comparison is made between the contents of the selected CAR and the contents of the B register. If any of the corresponding bits are not equal, a CAR check error has occurred. This CAR check error terminates the Pio task and initiates an internal interrupt.

Word count register. A Word Count Register is provided in each Pio. The Word Count Register is loaded with the contents of the word-count portion of the data table,  $\langle 2:15 \rangle$ . This register is decremented each time a data word is transferred from (to) the data table.

Scan control register. A Scan Control Register is provided in each Pio that has chaining ability. Scan Control register bits are stored in the first word of the first data table (bit positions 0 and 1) and in the second word (bit positions 0 and 1) of the second data table and all subsequent data tables in a chain.

The Scan Control Register controls the I/O device and the Pio operation at the end of the data table as follows: single scan of data table and stop with an interrupt; single scan of data table and stop (no interrupt); continuous scan of this data table or a different data table with an interrupt at the end of this table; and continuous scan of this data table or a different data table with no interrupt.

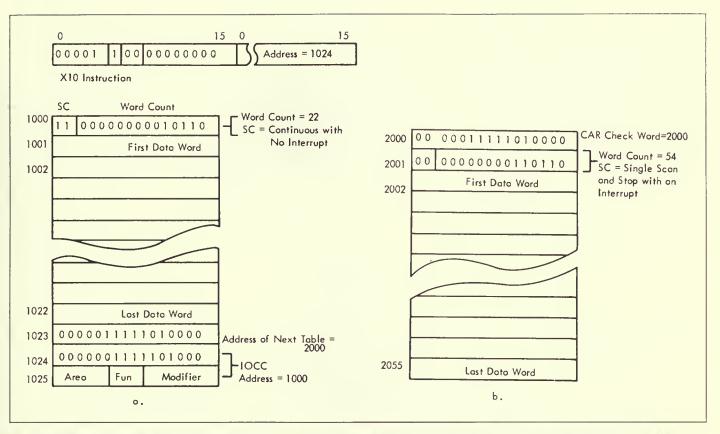

# The IO processor program operation

The sequence of steps for a Pio program is given below. The memory map or format of the program is shown in Fig. 7.

- Pc issues an XIO instruction which references the IOCC word and initializes Pio.

- 2 The Area Code and Modifier of the IOCC select the I/O device. Function specifies the type of operation (Initialize Read or Initialize Write, etc.).

<sup>1</sup>Not a completely arbitrary program fault to check, since processors are involved.

- 3 *a* The address portion of the IOCC word is stored in CAR for the selected Data Channel and I/O device.

- b A CAR check is made between the selected CAR and the B register.

- 4 A cycle steal is requested by Pio; CAR transfers to CAB.

- 5 CAB addresses core storage for the first word of the data table while CAR is being incremented by 1.

- 6 The first word of the data table contains

a Scan Control bits (bit positions 0 and 1)

b Word Count (bit position 2 to 15)

These are transferred to their respective registers in the I/O device. This is the end of the first cycle steal.

- 7 When another cycle-steal request from Pio occurs, CAR, which was incremented in step 5, now transfers the next higher address to CAB. CAB then addresses core storage while CAR is being incremented.

- 8 The first data word is transferred to or from the I/O device via the B register and Data Channel. The Word Count Register in the I/O device is decremented by I. This is the end of the second cycle-steal cycle.

Steps 7 and 8 now continue on a cycle-steal basis; that is, they occur as the I/O device requests data transfers. The CAR is incremented with each data transfer and the WCR is decremented. This sequence continues until the last data word of the data table is transferred. The last word transfer is sensed by the WCR reaching zero or through some indicator in the device. If the device does not have chaining ability, no more demands for data transfer are made until the device is reinitialized with another XIO instruction.

Chaining. These steps are for the second and all subsequent data tables. See above for steps I through 8.

- 9 The contents of the word following the last data word in the first data table are transferred to CAR. This word must contain the address of the next data table.

- 10 *a* When the next cycle is requested, CAR is transferred to CAB to address core storage. The contents of the first word of the next data table is transferred to the B register. This word must contain the address of itself.

- 10 b CAR check is performed and CAR is incremented by I.

- 11 When the next cycle steal is requested, CAR is transferred to CAB and CAB addresses Mp. The Scan-control bits and Word-count bits are transferred from the second word of

Fig. 7. IBM 1800 data-channel tables for chaining memory maps. (a) First data table; (b) second data table. (Courtesy of International Business Machines Corporation.)

the data table to their respective registers. CAR is incremented by 1.

- 12 Data are transferred to (from) the I/O device on a cyclesteal basis via the B register and the Data Channel. CAB addresses core storage to transfer a data word to the B register. Each time CAB addresses core storage, CAR is incremented by 1. When the next cycle-steal request occurs, CAR is transferred to CAB. The Word-count Register is decremented for each word transferred.

- 13 When the last data character is transferred (word count is decremented to zero), operation will continue as specified by the Scan Control Register. (See above section for *Scan-Control Register.*)

#### Special data channels

The four Pio types for special functions are:

- 1 Analog input (block data transfers, and comparisons of analog inputs for limits)

- 2 Digital input/output

- 3 Analog output

- 4 Digital output

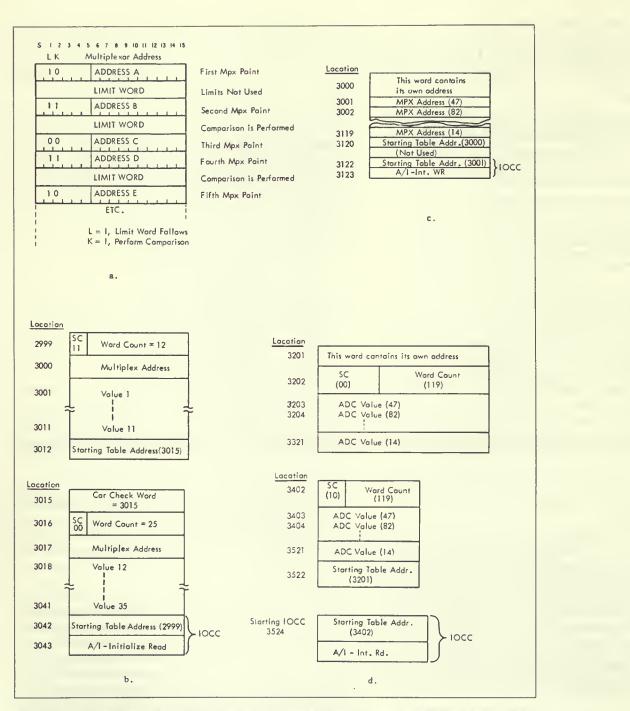

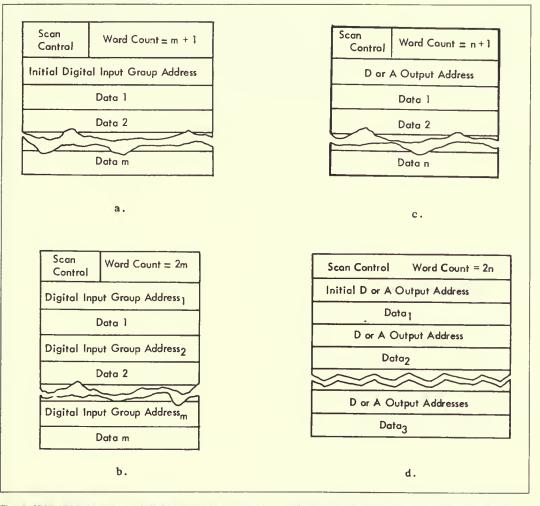

Analog-input data channels. Memory maps (Fig. 8a and b) illustrate the command formats interpreted in the Analog Data Channel programs. A list of limit values is placed in a table (Fig. 8a), and each analog input is compared with the limits. The operation sequence is: Read a specific addressed analog voltage, called the multiplex<sup>1</sup> point (mpx); compare the input voltage with the limits stored in the table following the analog address (the limit word contains a high and low value in bits  $\langle 0:7 \rangle$  and  $\langle 8:15 \rangle$ , respec-

$^1{\rm The}$  IBM multiplexor is an S which allows multiple inputs to be read into the T(Analog to Digital Converter) sequentially.

Fig. 8. IBM 1800 data-channel analog-input instruction format and memory maps. (a) Multiplexor address table with limit words for comparisons. (b) Data table, chained sequential control. (c) Multiplexor address table, random addressing. (d) Analog-to-digital converter storage tables, random addressing (used with a second data channel).

Fig. 9. IBM 1800 data-channel digital or analog-output instruction formats and memory maps. (a) Digital input, sequential; (b) digital input, random addressing; (c) digital or analog output, sequential; (d) digital or analog output, random addressing. (Courtesy of International Business Machines Corporation.)

tively); and if the analog-input value lies outside the limit range, initiate an interrupt.

Figure 8b describes a second use of this data channel. Pio accepts a sequence of analog inputs and packs them into a table following the address initiation instruction. The analog inputs from the T's are either fixed or selected in a cyclic fashion from a Multiplexor.

Two Pio's can be used concurrently: One Pio controls the input from a series of analog-input addresses (Fig. 8c); the second Pio packs the corresponding analog values in a second table (Fig. 8d). Digital-input data channels. Digital parameters or events can be read into Mp under the control of a Digital-input Data Channel. The memory map (Fig. 9a) shows the control format for selecting and inputting a block or sequence of external data. The memory map (Fig. 9b) illustrates a more general ability to address inputs at random and read them into succeeding Mp locations.

Digital- and analog-output data channels. Memory maps (Fig. 9c and d) show the program format used by the Digital- or Analogoutput Data Channels. These channels output selected data points to external analog or digital K's. This Pio is similar to the Digitalinput Data Channel.

# Conclusions

We have tried to show a typical, third-generation computer used for process control. Many of the facilities the 1800 possesses are general. The Pio's are rather special, designed to monitor and control a process, independent of Pc. Although the Pio's are powerful (by providing parallel data transmission), their use, like other multiprocessing systems, is nontrivial. The Pc ISP is fairly straightforward, and one should write a program using it to appreciate its simplicity.

### APPENDIX 1 THE IBM 1800 ISP DESCRIPTION

| I BM                                                        | 1 1800 ISP Description                                                                          |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                                                             |                                                                                                 |

| Pc State                                                    |                                                                                                 |

| A<0:15>                                                     | Accumulator                                                                                     |

| Q<0:15>                                                     | Accumulator Extension for multiplier, cuotient and double<br>length                             |

| 1<0:15>                                                     | Instruction Location Counter                                                                    |

| XR[1:3]<0:15>                                               | Index Registers                                                                                 |

| 0 v                                                         | Overflow Indicator                                                                              |

| с                                                           | Carry Indicator                                                                                 |

| Run                                                         | denotes running computer                                                                        |

| Mp State                                                    |                                                                                                 |

| M[0:FFFF <sub>16</sub> ] <p,s,0:15></p,s,0:15>              | Mp with Parity and Protect bits                                                                 |

| Pc Console State                                            |                                                                                                 |

| Check Stop Switch                                           | Pc stops if storage protect violation occurs                                                    |

| WSPB Switch                                                 | Write Storage Protect Bits; enables the writing of bits in a word                               |

| SPV Indicator                                               | Storage Protect Violation indicator; set to 1 if a memory reference is made to a protected word |

| Instruction Format                                          |                                                                                                 |

| instruction/i[0:1]<0;15>                                    |                                                                                                 |

| op<0:4> := i[0]<0:4>                                        | operation code                                                                                  |

| shop<0:7> := op⊡i[0]<5,8,9>                                 | shift operation code count                                                                      |

| f := i[0]<5>                                                | format; specifies a 1 or 2 word instruction                                                     |

| t<0:1> := i[0]<6:7>                                         | tag: index register specification                                                               |

| d<8:15> := i[0]<8:15>                                       | displacement or short address                                                                   |

| dsgn<0:15>:= sign, extend (d<8>⊃d<9:15>)                    |                                                                                                 |

| a⊲0:15> := i[1]⊲0:15>                                       | address                                                                                         |

| ia := i[0]<8>                                               | indirect address bit                                                                            |

| bo := i[0]<8>                                               | branch out bit                                                                                  |

| cond<0:5> :≖ i[0]<10:15>                                    | conditions for test                                                                             |

| Effective Address Calculation Process                       |                                                                                                 |

| z<0:15>:= (                                                 | effective address                                                                               |

| $(t = 0) \land \neg f \rightarrow (dsgn + 1);$              | 1 word, relative                                                                                |

| $(t \neq 0) \land \neg f \rightarrow (dsgn + XR[t]);$       | 1 word, relative, indexed                                                                       |

| $(t = 0) \land f \land \neg ia \rightarrow a;$              | 2 word, direct                                                                                  |

| $(t \neq 0) \land f \land \neg ia \rightarrow (a + XR[t]);$ | 2 word, direct, indexed                                                                         |

| $(t = 0) \land f \land ia \rightarrow M[a];$                | 2 word, indirect                                                                                |

| $(t \neq 0) \land f \land ia \rightarrow (M[a + XR[t]]))$   | 2 word, indirect, indexed                                                                       |

| $z' < 0:15 > := (\neg f \rightarrow (dsgn + 1);$            | effective address for index register instructions                                               |

| f ∧ ¬ ia →a:<br>f ∧ ia →M[a])                               |                                                                                                 |

# APPENDIX 1 THE IBM 1800 ISP DESCRIPTION (Continued)

```

zd < 0:15 > := (\neg z < 15 > \rightarrow z + 1;

z < 15 > \rightarrow z)

xi < 0:15 := (\neg f \rightarrow dsgn;

f ∧ ¬ ia →a;

f \wedge ia \rightarrow M[a]

s<0:5> := (

(t = 0) \rightarrow d < 10:15>

(t \neq 0) \rightarrow XR[t] < 10:15 >)

Instruction Interpretation Process

Run \rightarrow (instruction[0:1] \leftarrow M[1:1 + 1]; next

\neg f \rightarrow (1 \leftarrow l + 1); f \rightarrow (1 \leftarrow l + 2); next

Instruction_execution)

Instruction Set and Instruction Execution Process

Instruction_execution := (

Load and Arithmetic

LO (:= op = 11000) \rightarrow (A \leftarrow M[z]);

LOO (:= op = 11001) \rightarrow (ADQ \leftarrow M[z]DM[zd]);

STO (:= op = 11010) \rightarrow (M[z] \leftarrow A);

STD (:= op = 11011) \rightarrow (M[z]\squareM[zd] \leftarrow A\squareQ);

A (:= op = 10000) \rightarrow (0v,C\squareA \leftarrow A + M[z]);

A0 (:= op = 10001) \rightarrow (0v, CDADQ \leftarrow ADO + M[z]DM[zd]);

S (:= op = 10010) \rightarrow (0v,C\squareA \leftarrow A - M[z]);

SO (:= op = 100]1) \rightarrow (Ov,CoAcQ \leftarrow AcQ - M[z]oM[zd]);

M \quad (:= op = 10100) \rightarrow (A \Box Q \leftarrow A \times M[z]);

0 (:= op = 10101) \rightarrow (0v,Q \leftarrow A\squareQ / M[z];

A \leftarrow A \square Q \mod M[z]);

Logical instructions

AND (:= op = 11100) \rightarrow (A \leftarrow A \land M[z]);

OR (:= op = 11101) \rightarrow (A \leftarrow A \lor M[z]);

EOR (:= op = 11110) \rightarrow (A \leftarrow A \oplus M[z]);

Compare

\mathsf{CMP} \ (:= \mathsf{op} = 10110) \to ((\mathsf{A} < \mathsf{M}[z]) \to (1 \leftarrow 1 + 1);

(A = M[z]) \rightarrow (1 \leftarrow 1 + 2));

\mathsf{OCM} \ (:= \mathsf{op} = \mathsf{10111}) \rightarrow ((\mathsf{A} \Box \mathsf{Q} < \mathsf{M}[\mathsf{z}] \Box \mathsf{M}[\mathsf{zd}]) \rightarrow (\mathsf{1} \leftarrow \mathsf{1} + \mathsf{1});

(A\Box Q = M[z]\Box M[zd]) \rightarrow (1 \leftarrow 1 + 2));

Shifts

SLA (:= shop = 00010\square0\square00) \rightarrow (

A \leftarrow A \ge 2^{S} {logical}; C \leftarrow A < -1>;

SLT (:= shop = 00010\Box0\Box10) \rightarrow (

A \square Q \leftarrow A \square Q \times 2^{S} \{ logical \}; C \leftarrow A < -1 > \};

SRA (:= shop = 00011\pm0\pm00) \rightarrow (A \leftarrow A / 2<sup>S</sup> {logical});

SRT (:= shop = 00011 \Box0 \Box10) \rightarrow (A\BoxQ \leftarrow A\BoxQ / 2<sup>S</sup>):

RTE (:= shop = 00011\square O \square 11) \rightarrow (A \square Q \leftarrow A \square Q / 2^{5} {rotate}):

SLCA(:= shop = 00010\square0\square01) \rightarrow (

```

```

process for locating second operand for double length

index increment

shift count calculation

fetch

1 or 2 word instruction

execute

load accumulator

double load

store accumulator

double store

add

double add

subtract

double subtract

multiply

divide

logical and

logical or

logical exclusive or

compare

double compare

shift left logical

shift double left logical

shift right logical

shift right A and Q

rotate right A and Q

shift left and count A

```

APPENDIX 1 THE IBM 1800 ISP DESCRIPTION (Continued)

```

(t = 0) \rightarrow (A \leftarrow A \times 2^{S}; C \leftarrow A < s - I >);

(t \neq 0) \rightarrow (A \leftarrow \text{normalize}(A);

CmXR[t]<10:15> ← normalize_exponent(A);

XR[t] < 8,9 \leftarrow 0);

SLC (:= shop = 00010\pm0011) \rightarrow (\neg ((s = 0) \lor A<0>) \rightarrow (

shift left and count

(t = 0) \rightarrow (A \square Q \leftarrow A \square Q \times 2^{5}; C \leftarrow A < s - l >);

(t \neq 0) \rightarrow (A \square Q \leftarrow normalize(A \square Q);

C□XR[t] ← normalize_exponent(A□Q))));

LOX (:= op = 01100) \rightarrow ((t = 0) \rightarrow (1 \leftarrow z<sup>1</sup>);

load index or instruction counter

(t \neq 0) \rightarrow (XR[t] \leftarrow z'));

STX (:= op = 01101) \rightarrow ((t = 0) \rightarrow (M[z'] \leftarrow 1);

store index or instruction counter

(t \neq 0) \rightarrow (M[z'] \leftarrow XR[t]));

STS (:= op = 00101) \rightarrow (

store status

(f \land bo) \rightarrow M[z] < P \rightarrow cond < 15;

\neg bo \rightarrow (M[z] < 8:15 \leftarrow 00000 \square \square Ov; \square Ov \leftarrow 00));

load status

0v \leftarrow i[0] < 15);

BSC (:= (op = 01001) \land \neg i < 9 \supset) \rightarrow (

branch or skip on condition

( skip_condition \land \neg f) \rightarrow (I \leftarrow I + I);

(\neg skip, condition \land f) \rightarrow (I \leftarrow z);

d < 15 \rightarrow 0v \leftarrow 0);

skip_condition := (

(-10v ∧ d<15>) v

overflow off

(\neg C \land d < 14 >) \lor

carry off

(A<15> ∧ d<13>) ∨

Accumulator even

((A > 0) \land d < 12) \lor

Accumulator greater than zero

(A<0> ∧ d<11>) ∨

Accumulator negative

((A=0) \land d<10>))

Accumulator sero

BOSC (:=(op = 01001) \land I<9>) \rightarrow (

branch out of interrupts

(skip_condition \land \neg f) \rightarrow (I \leftarrow I + 1; Interrupt \leftarrow I);

(\neg skip\_condition \land f) \rightarrow (1 \leftarrow z; Interrupt \leftarrow 1);

d < 15 > \rightarrow (0 \lor \leftarrow 0));

BSI (:= op = 01000) \rightarrow (

branch and store instruction register

\neg f \rightarrow (1 \leftarrow z + 1; M[z] \leftarrow 1);

f \rightarrow (d < 15 > \rightarrow 0v \leftarrow 0);

\negskip_condition \rightarrow (I \leftarrow z + 1; M[z] \leftarrow I));

MDX (:= op = 01110) \rightarrow (

modify index and skip

(t = 0) \land \neg f \rightarrow (I \leftarrow I + dsgn);

local branch

(t = 0) \land f \rightarrow (M[a] \leftarrow M[a] + dsgn;

(Msum=0) \lor (M[0] < 0 > \oplus Msum < 0 >) \rightarrow (1 \leftarrow 1 + 1));

result zero or sign change

Msum<0:15> := (M[a] + dsgn)

(t \neq 0) \rightarrow (XR[t] \leftarrow XR[t] + xi;

(Xsum=0) \lor (XR[t] \leq 0 \geq \oplus Xsum \leq 0 \geq) \rightarrow (i \leftarrow i + 1)));

result zero or sign change

Xsum<0:15> := (XR[t] + dsgn)

Wait (:= i = 3000_{16}) \rightarrow (1 \leftarrow 1 - 1);

```

#### APPENDIX 1 THE IBM 1800 ISP DESCRIPTION (Continued)

```

10 Control Instruction:

XIO (:= op = 00001) \rightarrow (

Execute 1/0, not defined

IOCC[0:1] \leftarrow M[z] \square M[zd]; next

Execute_10_instruction)

)

end Instruction_execution

10 Instruction Format:

:= 1000[0]

address if IO data

10 Address<0:15>

1D Device or Area<0:4> := 10CC[1]<0:4>

io device name

10 Function<5:7> := 10CC[1]<5:7>

10 Modifier<8:25>

:= 1000[1]<8:15>

device function details

Device mode off line := (ID Function = 0)

Device mode write := (10 Function = 1)

Device mode read := (10 Function = 2)

Device mode sense Interrupt level := (IO Function = 3)

Oevice mode control := (10 Function = 4)

Device mode initialize write := (10 Function = 5)

Device mode initialize read := (10 Function = 6)

Device mode sense := (ID Function = 7)

```